stm32时钟系统

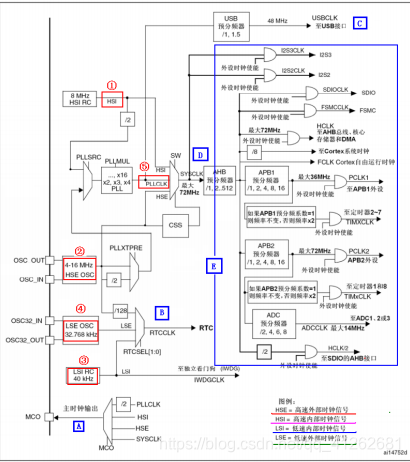

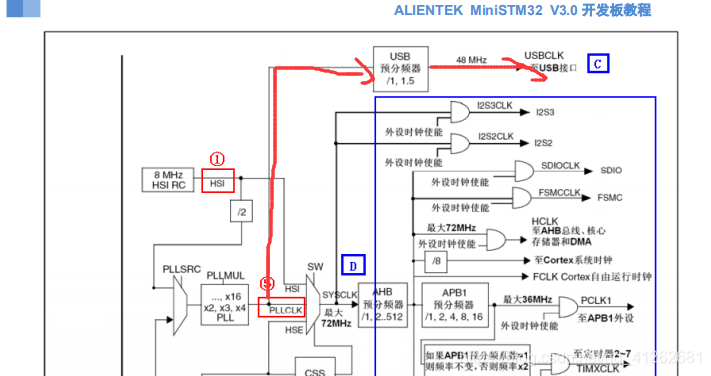

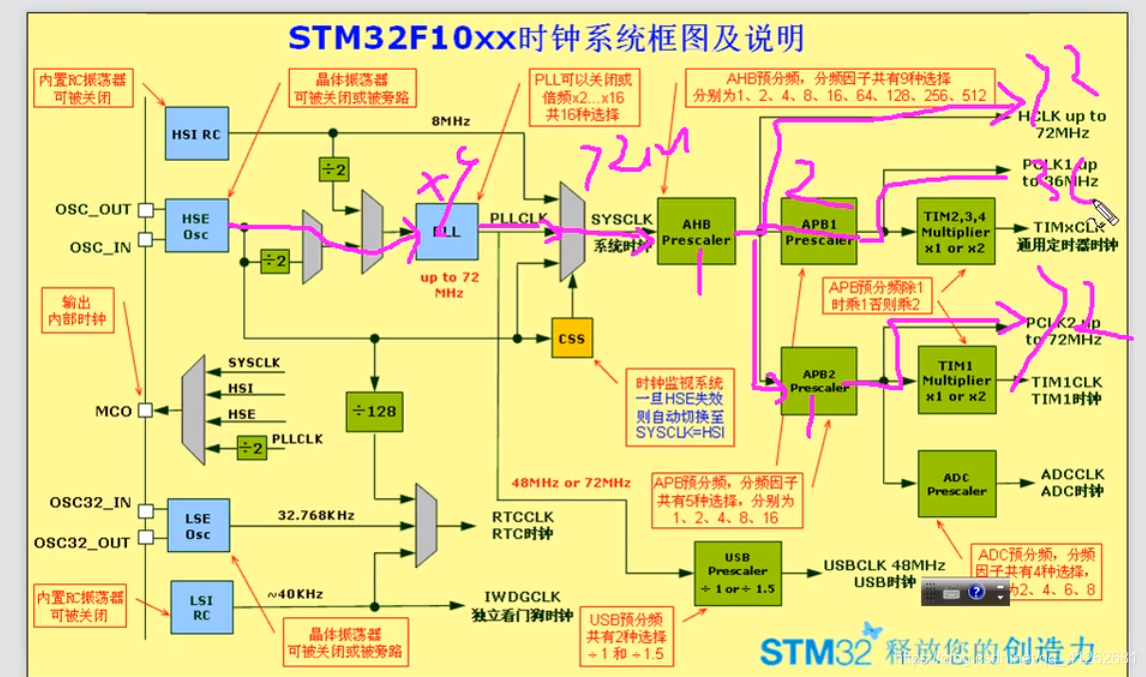

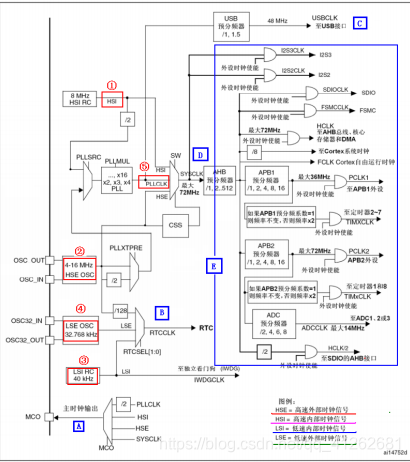

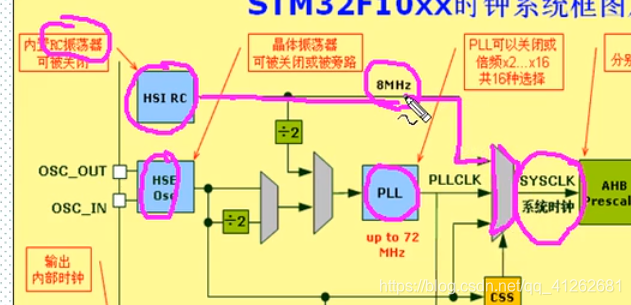

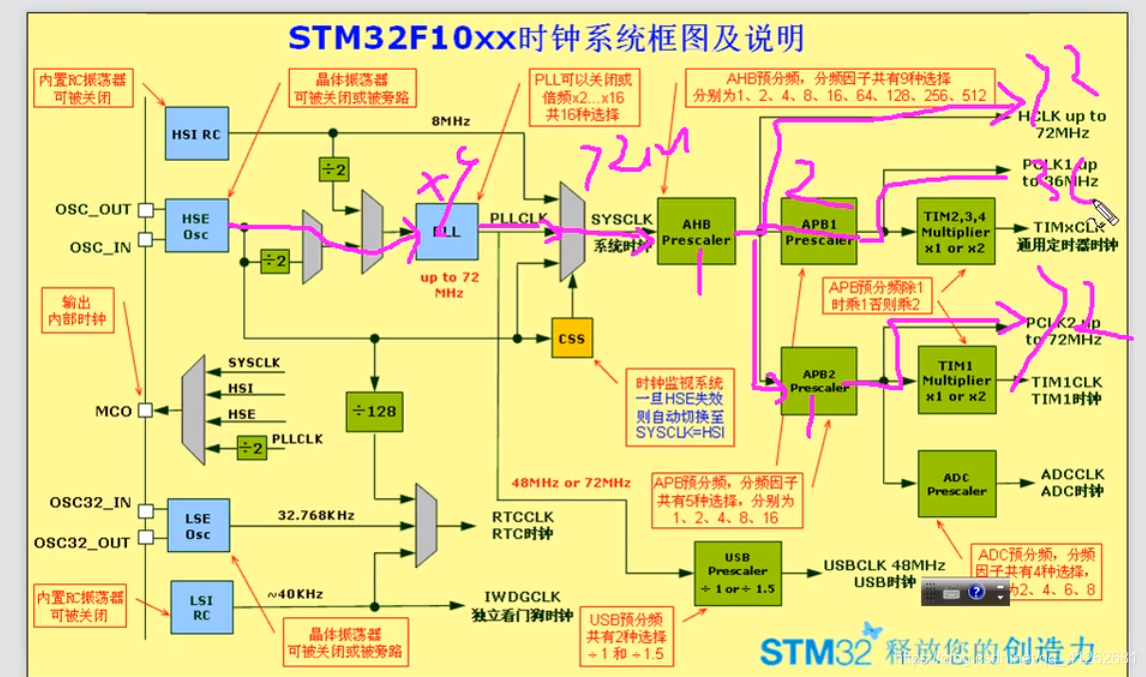

时钟系统的框图

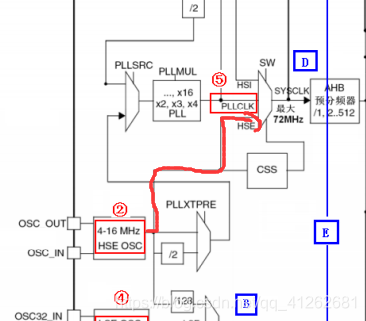

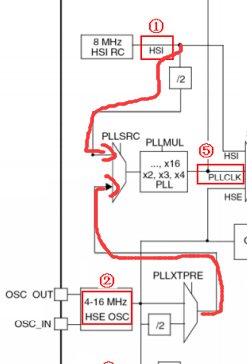

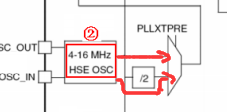

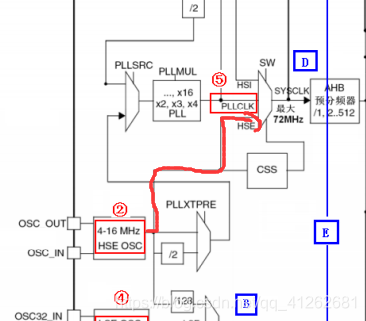

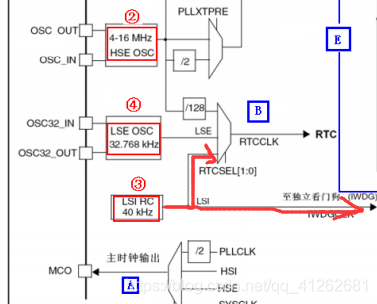

②、HSE(High Speed external) 是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为 4MHz~16MHz。 我们的开发板接的是 8M 的晶振。 可以作为第一个选择器选择输入和二分频选择输入

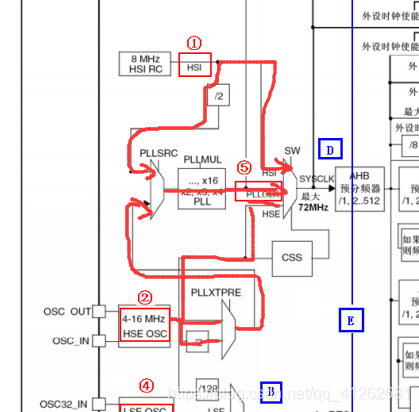

②、HSE(High Speed external) 是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为 4MHz~16MHz。 我们的开发板接的是 8M 的晶振。 可以作为第一个选择器选择输入和二分频选择输入  也可以作为系统时钟的选择

也可以作为系统时钟的选择  输出和HSI的二分频作为第二个选择器的选择输入

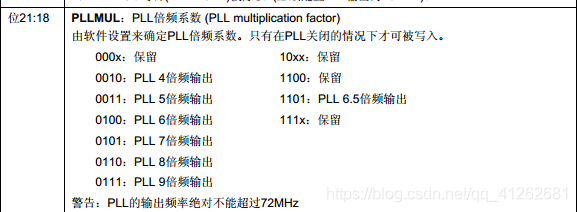

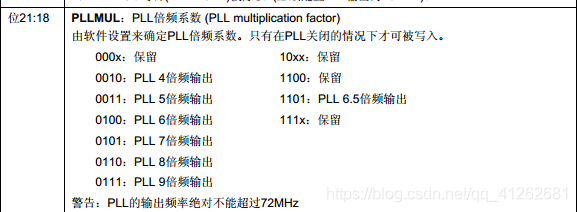

输出和HSI的二分频作为第二个选择器的选择输入  输出作为PLL的输入,PLL是锁相环也叫倍频器,可以放大2-16倍的频率 倍频器的输出可以作为系统时钟的选择 css是如果HSE突然出问题,就会自动切换到HSI

输出作为PLL的输入,PLL是锁相环也叫倍频器,可以放大2-16倍的频率 倍频器的输出可以作为系统时钟的选择 css是如果HSE突然出问题,就会自动切换到HSI

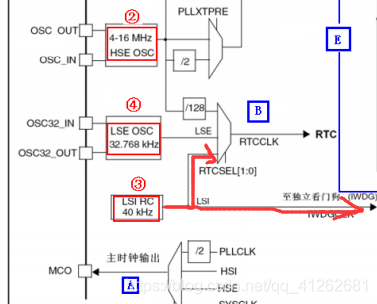

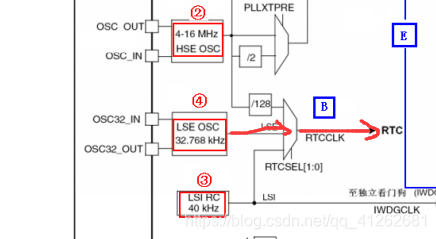

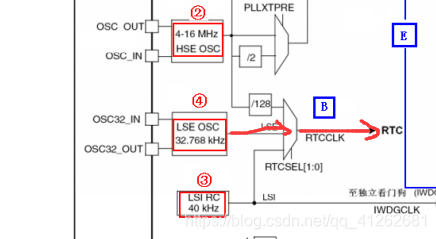

第一个选择器LSE或LSI或HSE的128分频都可以作为RTC时钟输入

第一个选择器LSE或LSI或HSE的128分频都可以作为RTC时钟输入  B.这里是RTC 时钟源,从图上可以看出,RTC 的时钟源可以选择 LSI,LSE,以及HSE 的 128 分频。

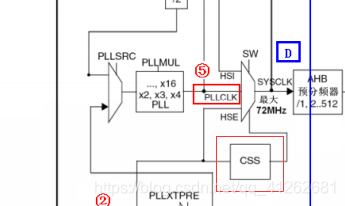

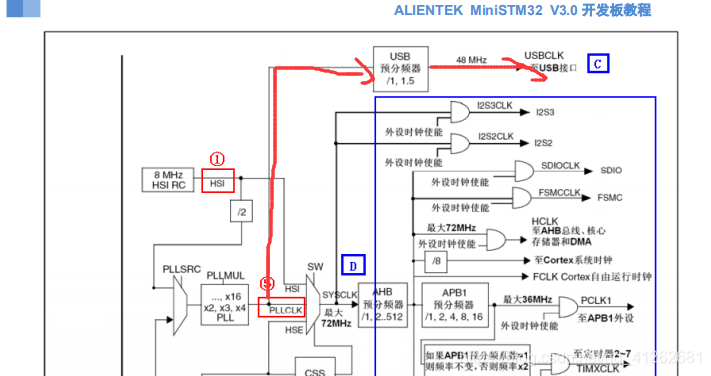

B.这里是RTC 时钟源,从图上可以看出,RTC 的时钟源可以选择 LSI,LSE,以及HSE 的 128 分频。  C. 从图中可以看出 C 处 USB 的时钟是来自 PLL 时钟源。STM32 中有一个全速功能的 USB 模块,其串行接口引擎需要一个频率为 48MHz 的时钟源。该时钟源只能从 PLL 输出端获取,可以选择为 1.5 分频或者 1 分频,也就是,当需要使用 USB模块时,PLL 必须使能,并且时钟频率配置为 48MHz 或 72MHz。

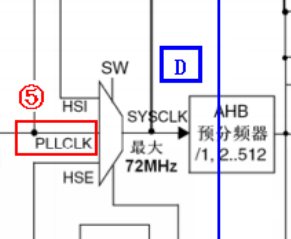

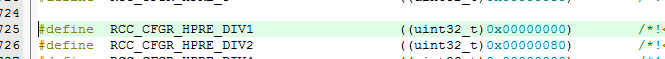

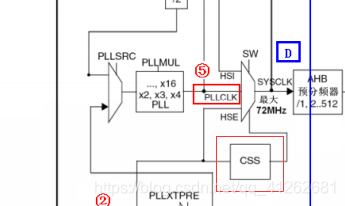

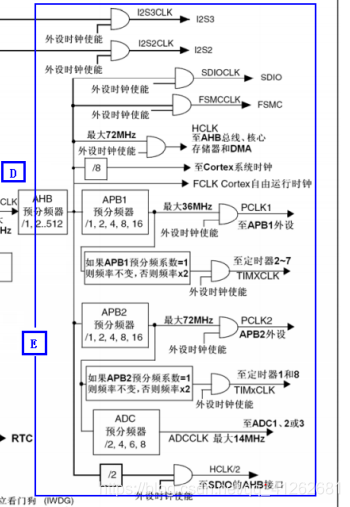

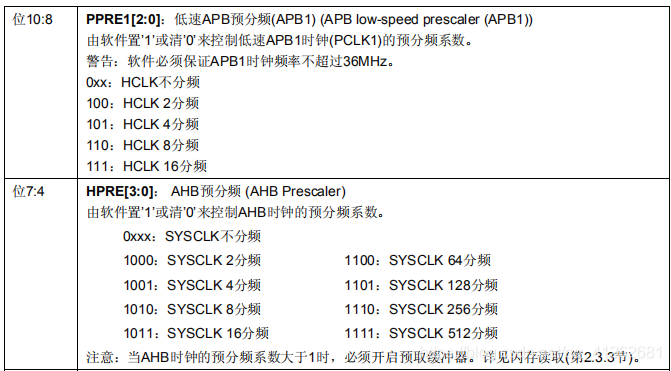

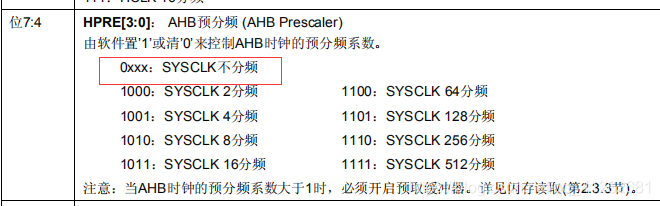

C. 从图中可以看出 C 处 USB 的时钟是来自 PLL 时钟源。STM32 中有一个全速功能的 USB 模块,其串行接口引擎需要一个频率为 48MHz 的时钟源。该时钟源只能从 PLL 输出端获取,可以选择为 1.5 分频或者 1 分频,也就是,当需要使用 USB模块时,PLL 必须使能,并且时钟频率配置为 48MHz 或 72MHz。  D. D 处就是 STM32 的系统时钟 SYSCLK,它是供 STM32 中绝大部分部件工作的时 钟源。系统时钟可选择为 PLL 输出、HSI 或者 HSE。系统时钟最大频率为 72MHz, 当然你也可以超频,不过一般情况为了系统稳定性是没有必要冒风险去超频的。 AHB预分频,分频因子有9种选择,分别为1,2,4,8,16,64,128,256,512

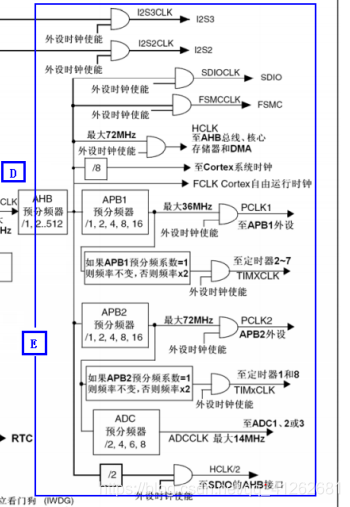

D. D 处就是 STM32 的系统时钟 SYSCLK,它是供 STM32 中绝大部分部件工作的时 钟源。系统时钟可选择为 PLL 输出、HSI 或者 HSE。系统时钟最大频率为 72MHz, 当然你也可以超频,不过一般情况为了系统稳定性是没有必要冒风险去超频的。 AHB预分频,分频因子有9种选择,分别为1,2,4,8,16,64,128,256,512  E. 这里的 E 处是指其他所有外设了。从时钟图上可以看出,其他所有外设的时钟最终来源都是 SYSCLK。SYSCLK 通过 AHB 分频器分频后送给各模块使用。这些模块包括:

E. 这里的 E 处是指其他所有外设了。从时钟图上可以看出,其他所有外设的时钟最终来源都是 SYSCLK。SYSCLK 通过 AHB 分频器分频后送给各模块使用。这些模块包括:  ①、AHB 总线、内核、内存和 DMA 使用的 HCLK 时钟。

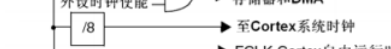

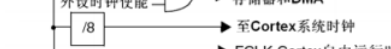

①、AHB 总线、内核、内存和 DMA 使用的 HCLK 时钟。  ②、通过 8 分频后送给 Cortex 的系统定时器时钟,也就是 systick 了。

②、通过 8 分频后送给 Cortex 的系统定时器时钟,也就是 systick 了。  ③、直接送给 Cortex 的空闲运行时钟 FCLK。

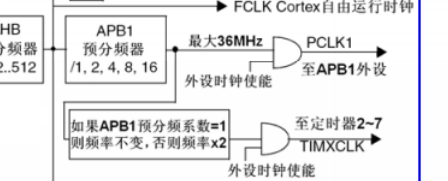

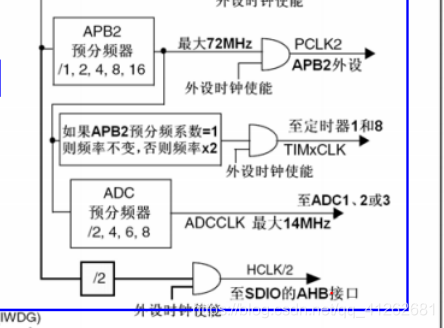

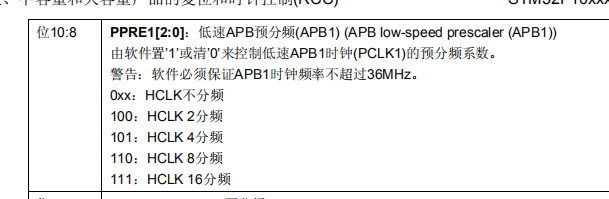

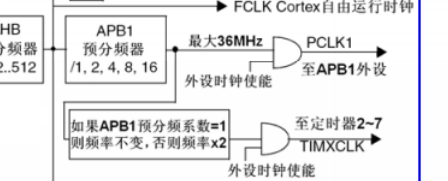

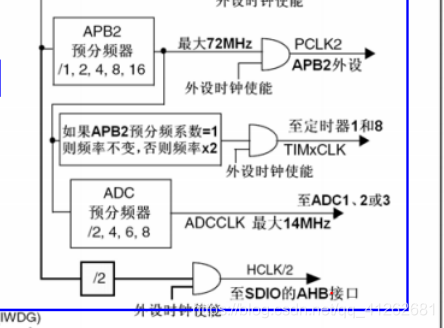

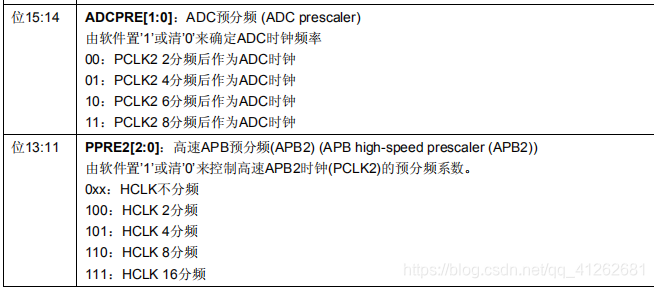

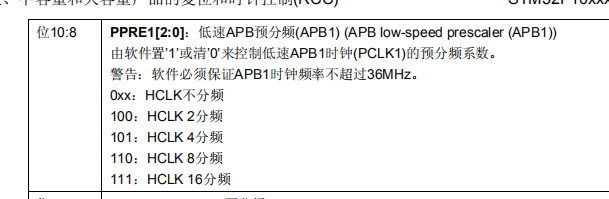

③、直接送给 Cortex 的空闲运行时钟 FCLK。  ④、送给 APB1 分频器。APB1 分频器输出一路供 APB1 外设使用(PCLK1,最大频率 36MHz),另一路送给定时器(Timer)2、3、4 倍频器使用

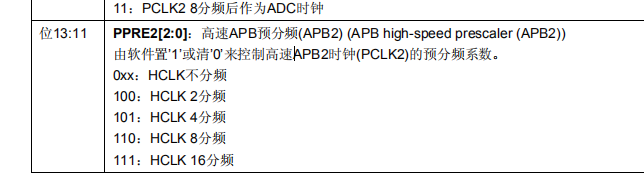

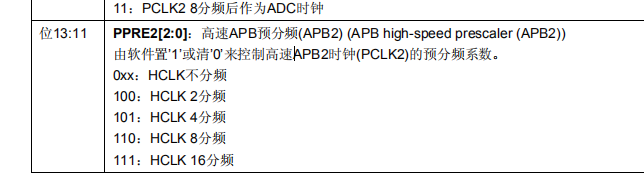

④、送给 APB1 分频器。APB1 分频器输出一路供 APB1 外设使用(PCLK1,最大频率 36MHz),另一路送给定时器(Timer)2、3、4 倍频器使用  ⑤、送给 APB2 分频器。APB2 分频器分频输出一路供 APB2 外设使用(PCLK2,最大频率 72MHz),另一路送给定时器(Timer)1 倍频器使用

⑤、送给 APB2 分频器。APB2 分频器分频输出一路供 APB2 外设使用(PCLK2,最大频率 72MHz),另一路送给定时器(Timer)1 倍频器使用

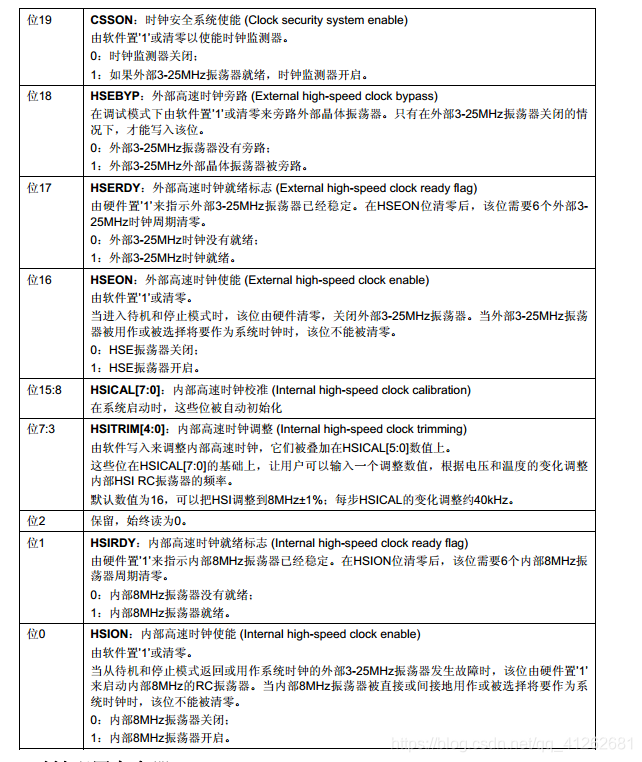

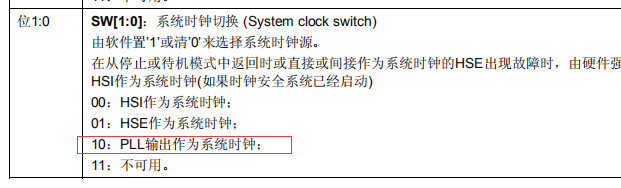

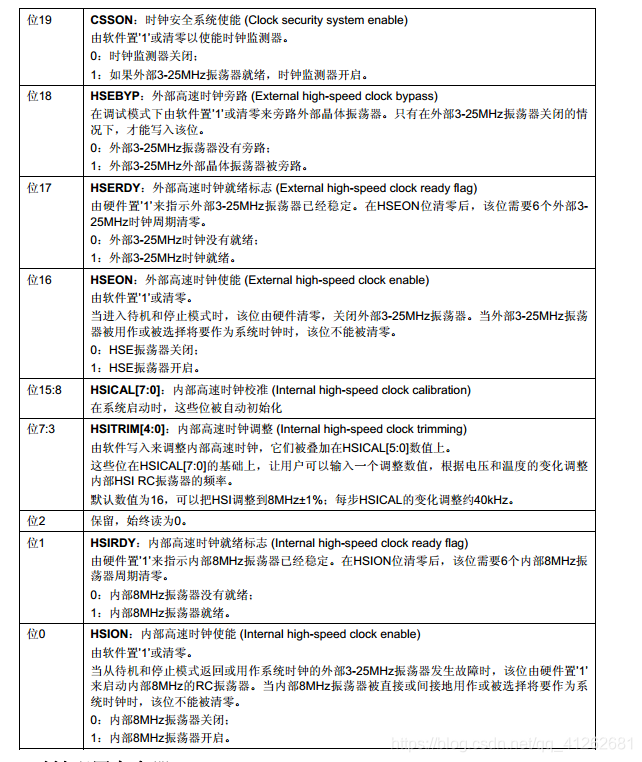

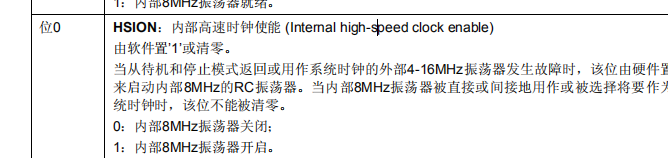

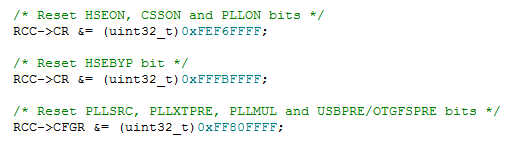

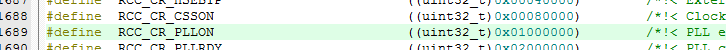

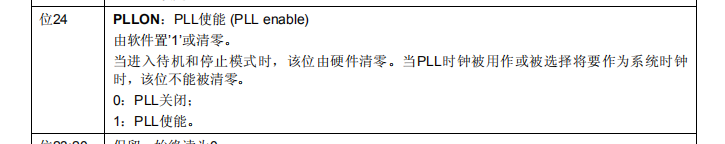

CR是对时钟源使能,使能且等待

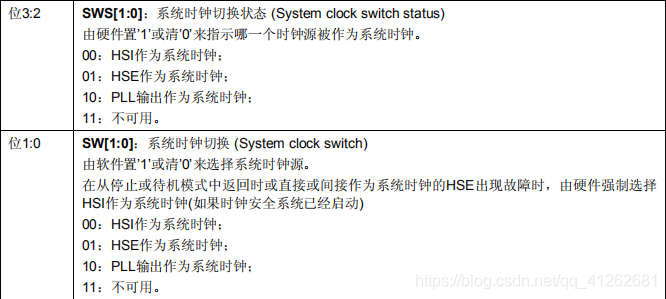

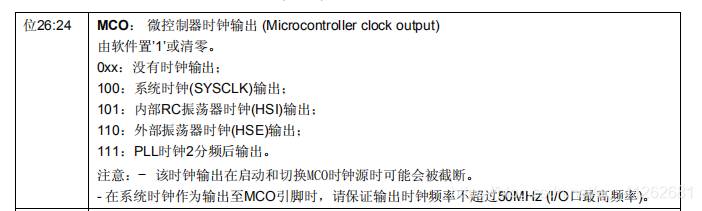

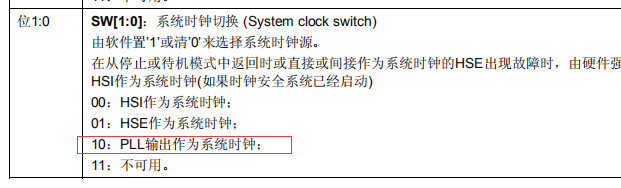

CR是对时钟源使能,使能且等待  CFGR对选择器进行设置,设置时钟源的选择

CFGR对选择器进行设置,设置时钟源的选择

几个重要的时钟 SYSCLK(系统时钟) AHB总线时钟 APB1总线时钟(低速):最高36MHZ APB2总线时钟(高速):最高72MHZ PLL时钟

几个重要的时钟 SYSCLK(系统时钟) AHB总线时钟 APB1总线时钟(低速):最高36MHZ APB2总线时钟(高速):最高72MHZ PLL时钟  1

1

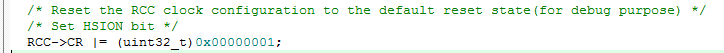

打开8MHZ的振荡器 2.将

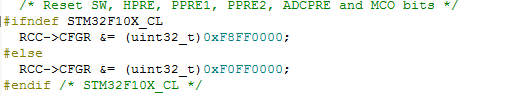

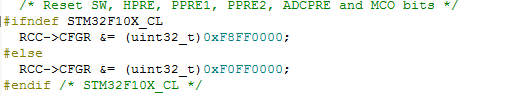

打开8MHZ的振荡器 2.将  将CFGR的24:27位,0:15位 置 0

将CFGR的24:27位,0:15位 置 0

也就是把SW, HPRE, PPRE1, PPRE2, ADCPRE and MCO全部关掉

也就是把SW, HPRE, PPRE1, PPRE2, ADCPRE and MCO全部关掉

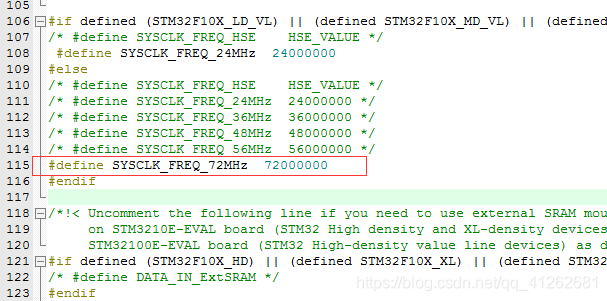

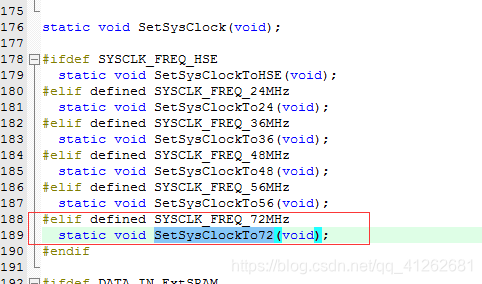

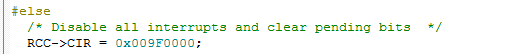

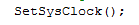

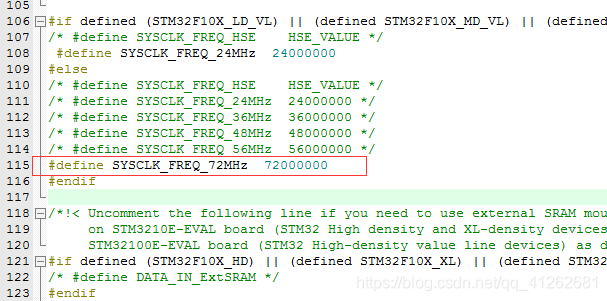

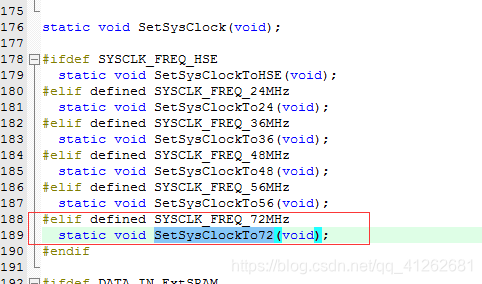

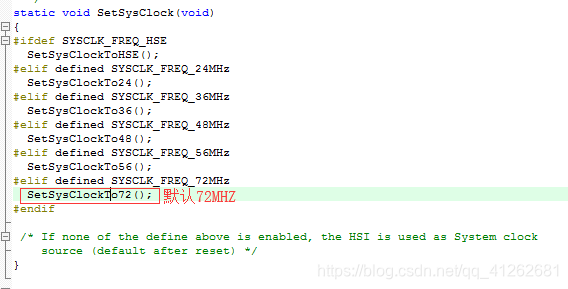

这里的定义决定了上面函数的调用

这里的定义决定了上面函数的调用

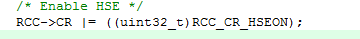

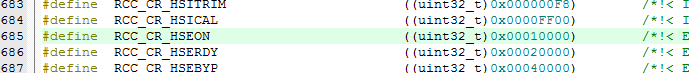

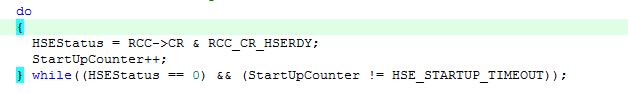

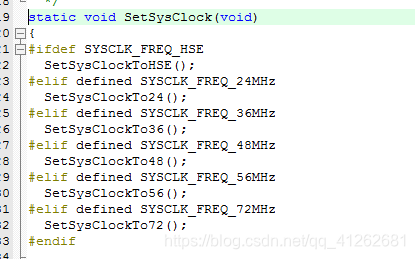

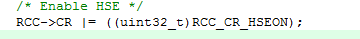

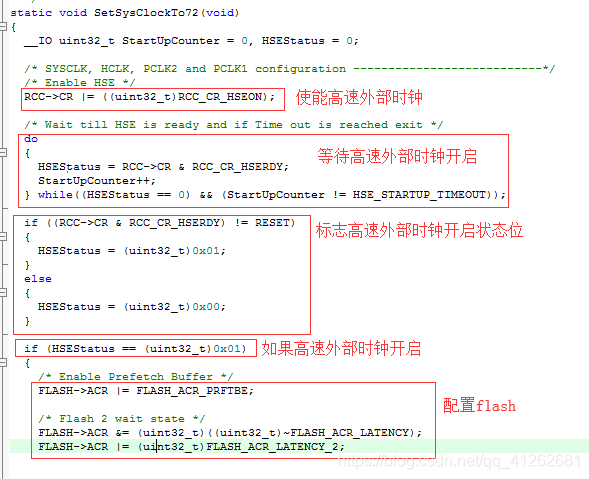

然后是SetSysClockTo72(void) 第一句

然后是SetSysClockTo72(void) 第一句

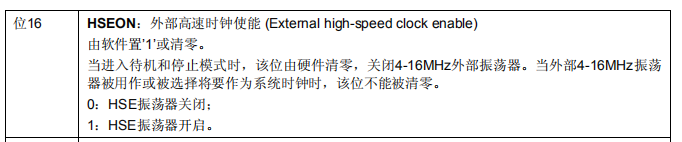

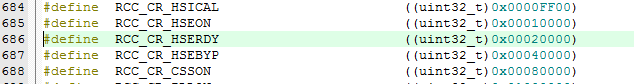

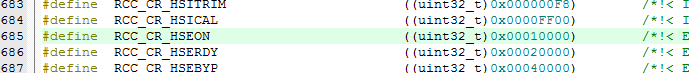

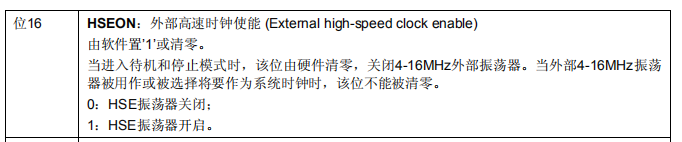

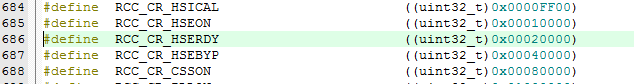

外部高速时钟使能位打开

外部高速时钟使能位打开

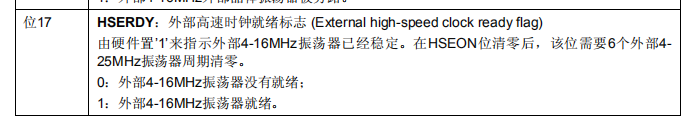

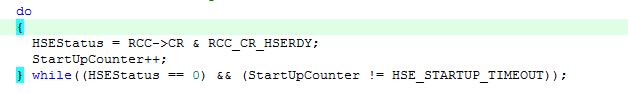

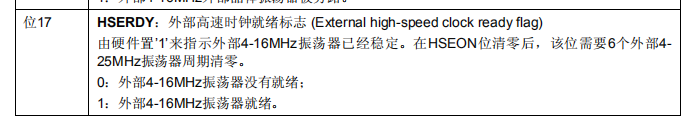

等待外部高速时钟使能就绪位置1

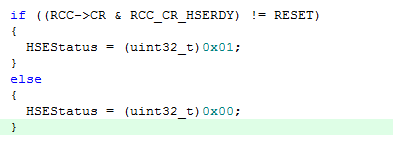

等待外部高速时钟使能就绪位置1  如果已经就绪状态位置1 如果状态位置1

如果已经就绪状态位置1 如果状态位置1

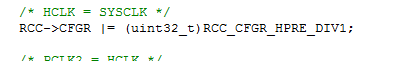

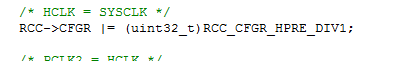

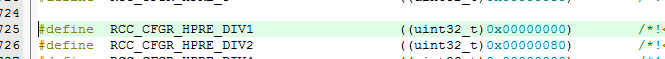

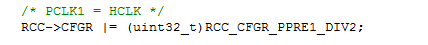

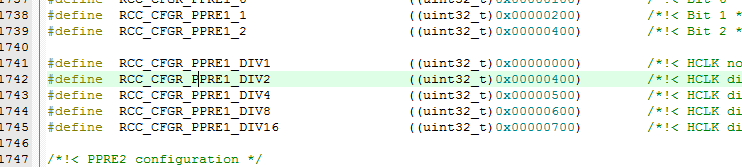

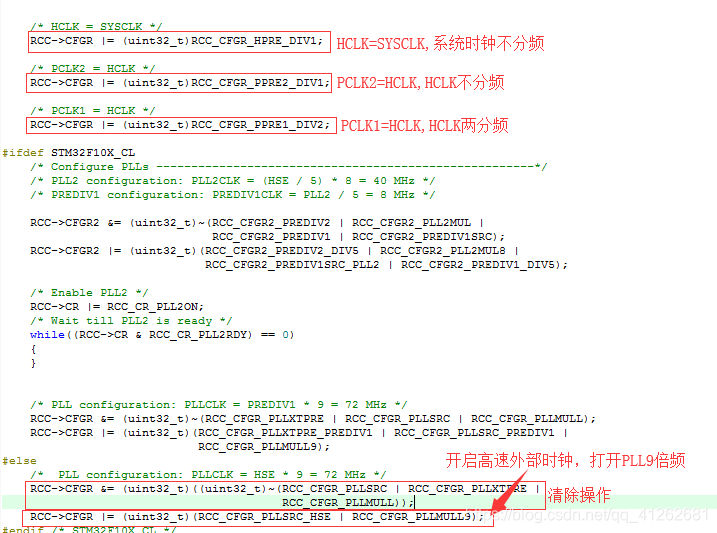

HCLK不分频

HCLK不分频

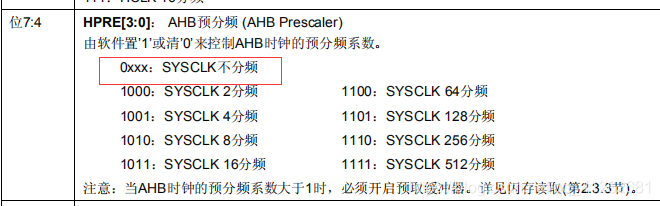

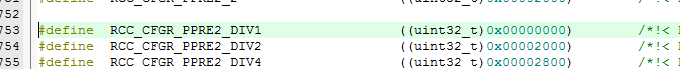

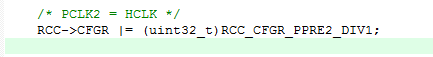

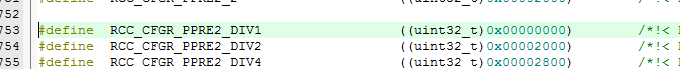

APB2不分频

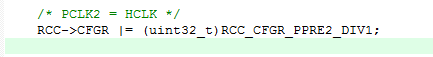

APB2不分频  APB1两分频

APB1两分频  最后

最后

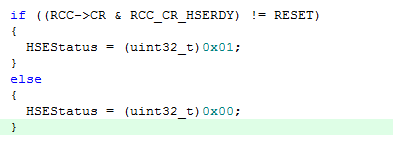

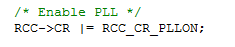

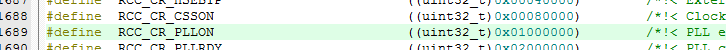

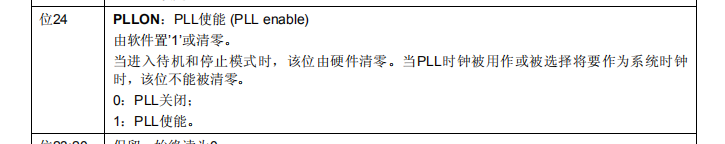

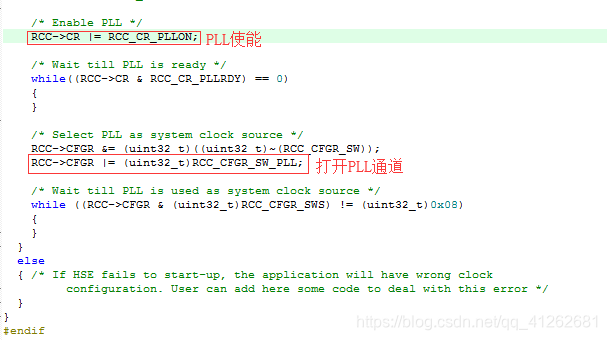

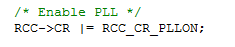

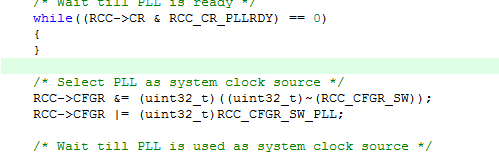

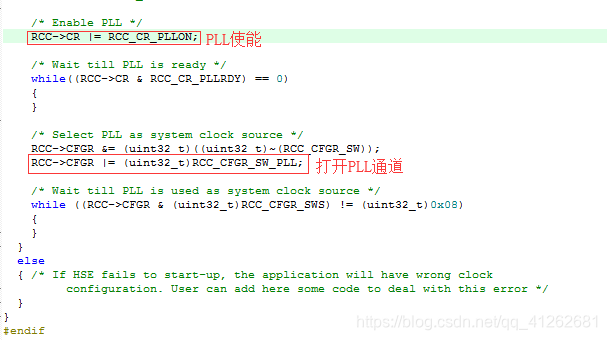

使能PLL

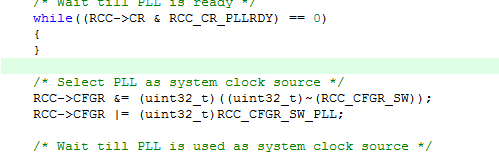

使能PLL  等待使能标志位

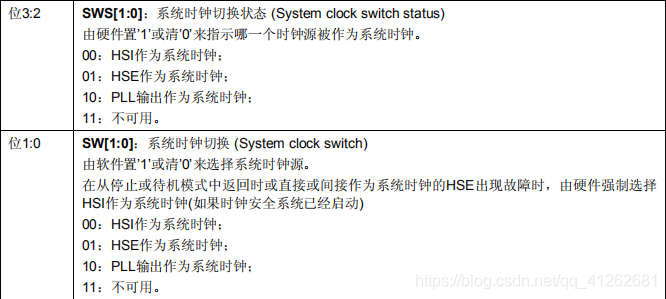

等待使能标志位  切换PLL作为系统时钟

切换PLL作为系统时钟

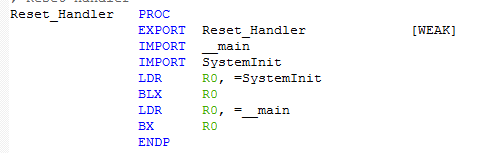

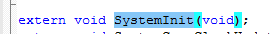

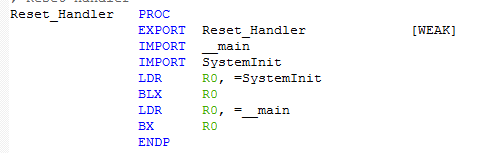

系统先执行SystemInit后执行main

系统先执行SystemInit后执行main

发布日期:2021-11-15 17:20:07

浏览次数:2

分类:技术文章

本文共 2497 字,大约阅读时间需要 8 分钟。

文章目录

时钟源

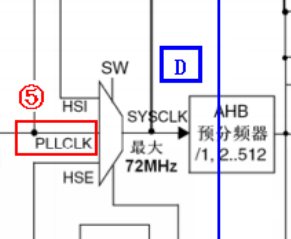

首先,有五个时钟源,图中红框部分

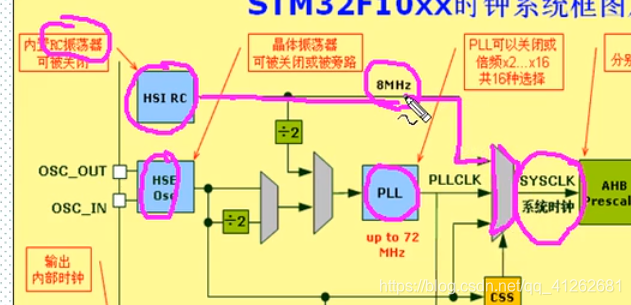

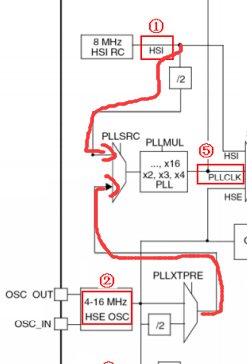

①、HSI(High Speed inter) RC是高速内部时钟,RC 振荡器,频率为 8MHz。(RC振荡器不够稳定) 可以作为系统时钟的选择 、 ②、HSE(High Speed external) 是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为 4MHz~16MHz。 我们的开发板接的是 8M 的晶振。 可以作为第一个选择器选择输入和二分频选择输入

②、HSE(High Speed external) 是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为 4MHz~16MHz。 我们的开发板接的是 8M 的晶振。 可以作为第一个选择器选择输入和二分频选择输入  也可以作为系统时钟的选择

也可以作为系统时钟的选择  输出和HSI的二分频作为第二个选择器的选择输入

输出和HSI的二分频作为第二个选择器的选择输入  输出作为PLL的输入,PLL是锁相环也叫倍频器,可以放大2-16倍的频率 倍频器的输出可以作为系统时钟的选择 css是如果HSE突然出问题,就会自动切换到HSI

输出作为PLL的输入,PLL是锁相环也叫倍频器,可以放大2-16倍的频率 倍频器的输出可以作为系统时钟的选择 css是如果HSE突然出问题,就会自动切换到HSI

③、LSI (low speed inter)是低速内部时钟,RC 振荡器,频率为 40kHz。独立看门狗的时钟源只能是 LSI,同时 LSI 还可以作为 RTC 的时钟源。

④、LSE 是低速外部时钟,接频率为 32.768kHz 的石英晶体。这个主要是 RTC 的时钟源。

第一个选择器LSE或LSI或HSE的128分频都可以作为RTC时钟输入

第一个选择器LSE或LSI或HSE的128分频都可以作为RTC时钟输入 ⑤、PLL 为锁相环倍频输出,其时钟输入源可选择为 HSI/2、HSE 或者 HSE/2。倍频可选择为2~16 倍,但是其输出频率最大不得超过 72MHz

B.这里是RTC 时钟源,从图上可以看出,RTC 的时钟源可以选择 LSI,LSE,以及HSE 的 128 分频。

B.这里是RTC 时钟源,从图上可以看出,RTC 的时钟源可以选择 LSI,LSE,以及HSE 的 128 分频。  C. 从图中可以看出 C 处 USB 的时钟是来自 PLL 时钟源。STM32 中有一个全速功能的 USB 模块,其串行接口引擎需要一个频率为 48MHz 的时钟源。该时钟源只能从 PLL 输出端获取,可以选择为 1.5 分频或者 1 分频,也就是,当需要使用 USB模块时,PLL 必须使能,并且时钟频率配置为 48MHz 或 72MHz。

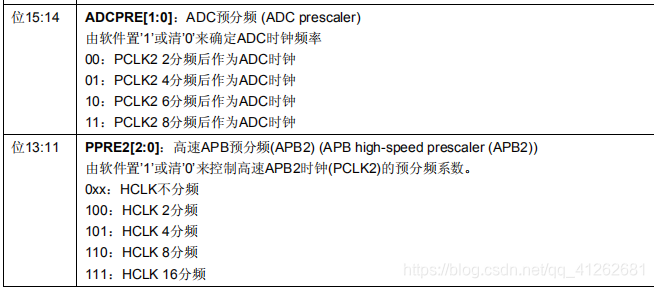

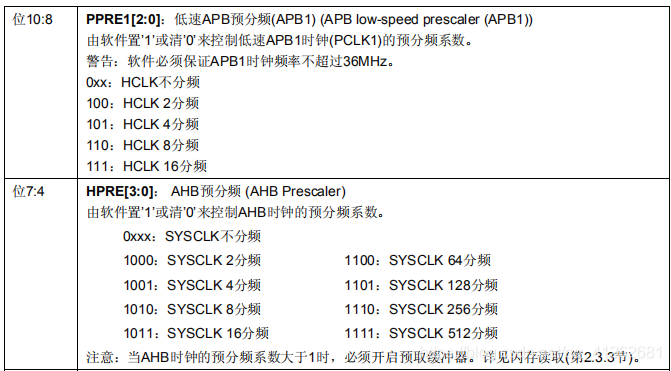

C. 从图中可以看出 C 处 USB 的时钟是来自 PLL 时钟源。STM32 中有一个全速功能的 USB 模块,其串行接口引擎需要一个频率为 48MHz 的时钟源。该时钟源只能从 PLL 输出端获取,可以选择为 1.5 分频或者 1 分频,也就是,当需要使用 USB模块时,PLL 必须使能,并且时钟频率配置为 48MHz 或 72MHz。  D. D 处就是 STM32 的系统时钟 SYSCLK,它是供 STM32 中绝大部分部件工作的时 钟源。系统时钟可选择为 PLL 输出、HSI 或者 HSE。系统时钟最大频率为 72MHz, 当然你也可以超频,不过一般情况为了系统稳定性是没有必要冒风险去超频的。 AHB预分频,分频因子有9种选择,分别为1,2,4,8,16,64,128,256,512

D. D 处就是 STM32 的系统时钟 SYSCLK,它是供 STM32 中绝大部分部件工作的时 钟源。系统时钟可选择为 PLL 输出、HSI 或者 HSE。系统时钟最大频率为 72MHz, 当然你也可以超频,不过一般情况为了系统稳定性是没有必要冒风险去超频的。 AHB预分频,分频因子有9种选择,分别为1,2,4,8,16,64,128,256,512  E. 这里的 E 处是指其他所有外设了。从时钟图上可以看出,其他所有外设的时钟最终来源都是 SYSCLK。SYSCLK 通过 AHB 分频器分频后送给各模块使用。这些模块包括:

E. 这里的 E 处是指其他所有外设了。从时钟图上可以看出,其他所有外设的时钟最终来源都是 SYSCLK。SYSCLK 通过 AHB 分频器分频后送给各模块使用。这些模块包括:  ①、AHB 总线、内核、内存和 DMA 使用的 HCLK 时钟。

①、AHB 总线、内核、内存和 DMA 使用的 HCLK 时钟。  ②、通过 8 分频后送给 Cortex 的系统定时器时钟,也就是 systick 了。

②、通过 8 分频后送给 Cortex 的系统定时器时钟,也就是 systick 了。  ③、直接送给 Cortex 的空闲运行时钟 FCLK。

③、直接送给 Cortex 的空闲运行时钟 FCLK。  ④、送给 APB1 分频器。APB1 分频器输出一路供 APB1 外设使用(PCLK1,最大频率 36MHz),另一路送给定时器(Timer)2、3、4 倍频器使用

④、送给 APB1 分频器。APB1 分频器输出一路供 APB1 外设使用(PCLK1,最大频率 36MHz),另一路送给定时器(Timer)2、3、4 倍频器使用  ⑤、送给 APB2 分频器。APB2 分频器分频输出一路供 APB2 外设使用(PCLK2,最大频率 72MHz),另一路送给定时器(Timer)1 倍频器使用

⑤、送给 APB2 分频器。APB2 分频器分频输出一路供 APB2 外设使用(PCLK2,最大频率 72MHz),另一路送给定时器(Timer)1 倍频器使用

时钟知识总结

1.5个时钟源

外部时钟源:HSE,LSE HSE来自外接的谐振器或外部时钟源 LSE来自石英晶体 HSI和LSI来源于RC振荡器 PLL来源于HSI/2,HSE或HSE/2系统时钟来源于三个时钟源HSI,HSE,PLL

2.时钟频率 高速时钟源 HSE:频率范围为4MHz-16MHz HSI:频率为8MHz PLL:频率不超过72Mhz 低速时钟源 LSI:频率范围为40khz LSE:频率范围为32.768khz3.时钟应用

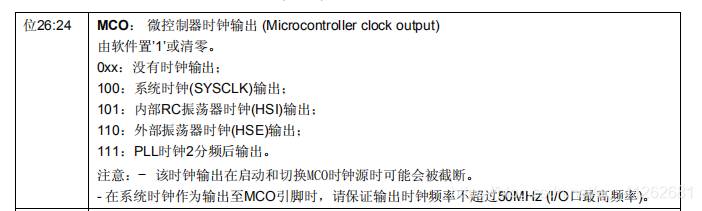

RTC来源于LSI,LSE或HSE的分频 独立看门狗(IWDG)时钟源只能来自于LSI USB时钟源来自于PLL MCO(stm32的一个IO用来时钟输出)时钟源来自PLL/2,HSI,HSE或时钟系统 除了以上的其他所有外设的时钟源都来自系统时钟,而系统时钟来自PLL,HSI或者HSE,不超过72MHZ 在任何一个外设使用之前,必须首先使能相应的时钟寄存器

RCC相关寄存器配置

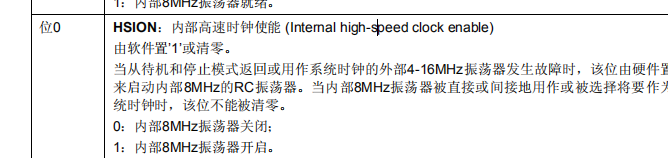

CR是对时钟源使能,使能且等待

CR是对时钟源使能,使能且等待  CFGR对选择器进行设置,设置时钟源的选择

CFGR对选择器进行设置,设置时钟源的选择

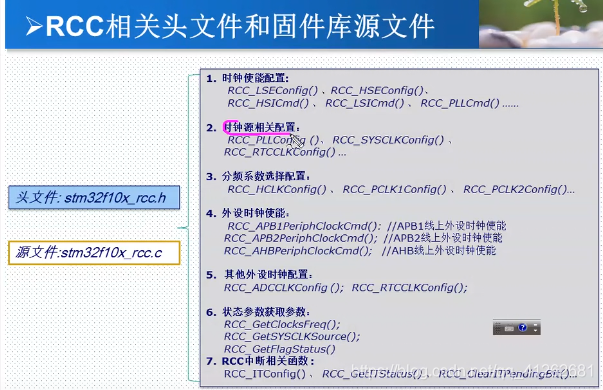

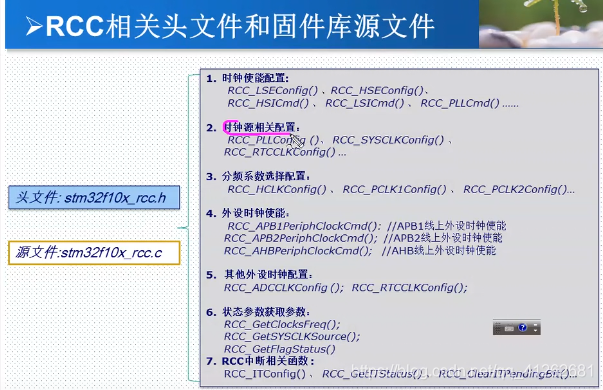

库函数

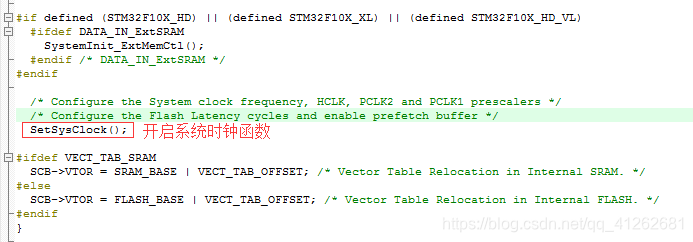

几个重要的时钟 SYSCLK(系统时钟) AHB总线时钟 APB1总线时钟(低速):最高36MHZ APB2总线时钟(高速):最高72MHZ PLL时钟

几个重要的时钟 SYSCLK(系统时钟) AHB总线时钟 APB1总线时钟(低速):最高36MHZ APB2总线时钟(高速):最高72MHZ PLL时钟 系统时钟初始化函数systeminit()

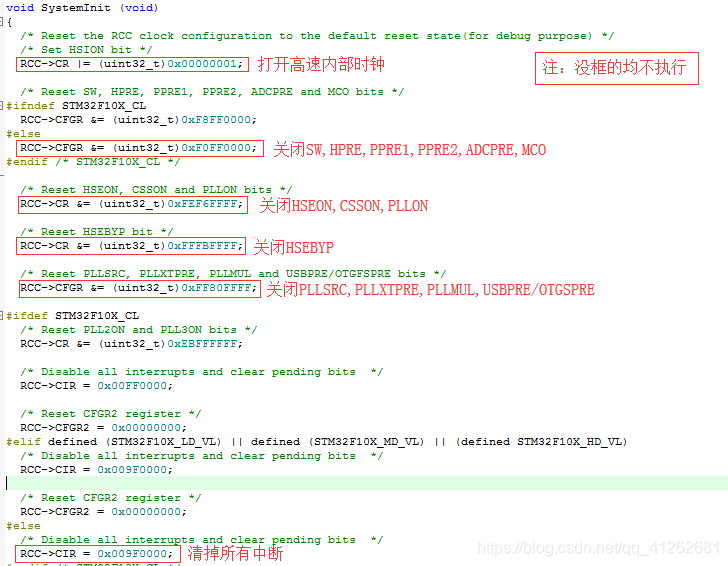

分析systeminit函数

1

1

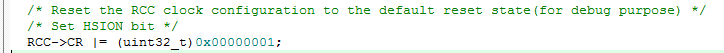

打开8MHZ的振荡器 2.将

打开8MHZ的振荡器 2.将  将CFGR的24:27位,0:15位 置 0

将CFGR的24:27位,0:15位 置 0

也就是把SW, HPRE, PPRE1, PPRE2, ADCPRE and MCO全部关掉

也就是把SW, HPRE, PPRE1, PPRE2, ADCPRE and MCO全部关掉

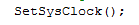

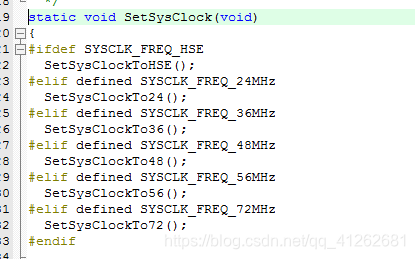

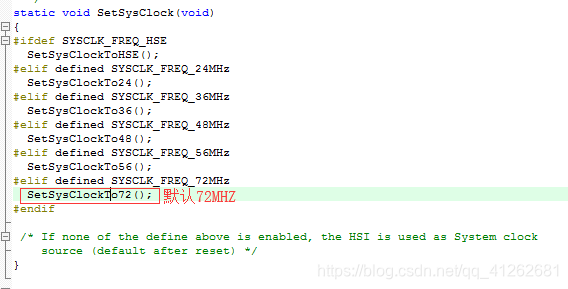

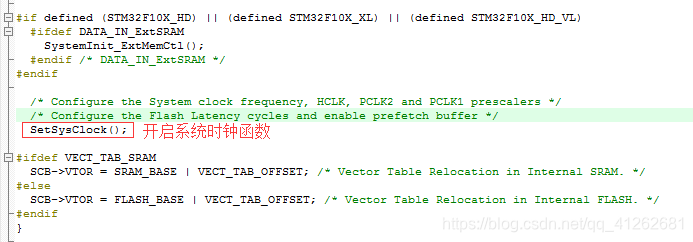

5.SetSysClock()

这里的定义决定了上面函数的调用

这里的定义决定了上面函数的调用

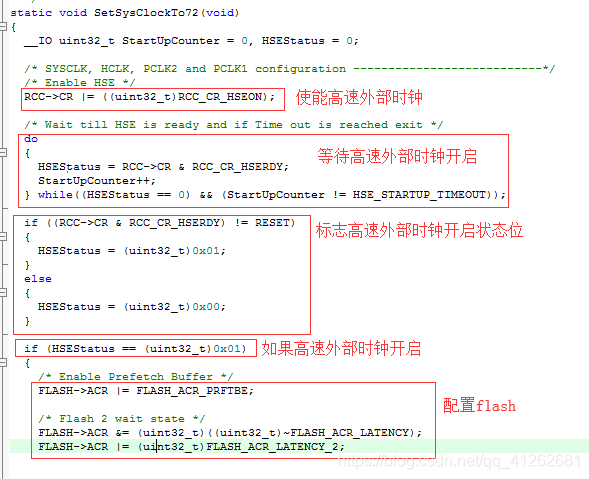

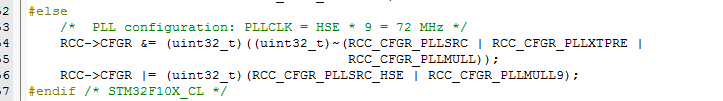

然后是SetSysClockTo72(void) 第一句

然后是SetSysClockTo72(void) 第一句

外部高速时钟使能位打开

外部高速时钟使能位打开 然后

等待外部高速时钟使能就绪位置1

等待外部高速时钟使能就绪位置1 然后

如果已经就绪状态位置1 如果状态位置1

如果已经就绪状态位置1 如果状态位置1

HCLK不分频

HCLK不分频

APB2不分频

APB2不分频

APB1两分频

APB1两分频

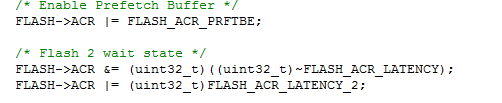

最后

最后

使能PLL

使能PLL  等待使能标志位

等待使能标志位  切换PLL作为系统时钟

切换PLL作为系统时钟 SetSysClockTo72()函数总过程

首先,打开HSE,然后等待就绪标志位 设置外设和时钟的关系 然后把时钟来源确定好 然后把PLL时钟打开,切换PLL为系统时钟来源SystemInit()函数全过程

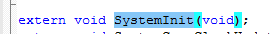

初始化中断自动调用SystemInit();

系统先执行SystemInit后执行main

系统先执行SystemInit后执行main 转载地址:https://blog.csdn.net/qq_41262681/article/details/94284703 如侵犯您的版权,请留言回复原文章的地址,我们会给您删除此文章,给您带来不便请您谅解!

发表评论

最新留言

能坚持,总会有不一样的收获!

[***.219.124.196]2024年04月11日 07时23分01秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

linux — Centos 7(第一天) 使用时出现的问题及解决方法

2019-04-27

数据结构 — 图的概述

2019-04-27

Centos 7 上 Eclipse 无法输入中文解决方法

2019-04-27

数据结构 — 图之邻接表存储创建和深度优先遍历

2019-04-27

Centos 7 — Gedit 配色方案

2019-04-27

数据结构 — 图 之 广度优先遍历

2019-04-27

数据结构 — 图 之 MST(最小生成树 — prim算法 )

2019-04-27

数据结构 — 图 之 MPT(最短路径 — dijkstra算法 )

2019-04-27

数据结构 — 7.有向图的创建及出入度的计算

2019-04-27

数据结构 — 图 之 拓扑排序 (AOV网)

2019-04-27

数据结构 — 图 之 关键路径、关键活动 (文字表述)

2019-04-27

数据结构 — 树 与 二叉树、森林

2019-04-27

数据结构 — 二叉树(创建、遍历)java实现

2019-04-27

数据结构 — 查找(最基础)

2019-04-27

关于 自减运算符 (i--/--j)在 循环(for与while)中的执行过程

2019-04-27

Jquery - Jquery 包装集

2019-04-27

python - 【用户、商品】【购买、浏览】数据处理

2019-04-27

python - sql + pandas 与 sqlite 结合

2019-04-27

python - 使用sql 分析(06 - 15)国内各省GDP

2019-04-27