UDP千兆以太网FPGA_verilog实现(一、知识搜集)

发布日期:2021-05-15 10:42:38

浏览次数:18

分类:技术文章

本文共 1325 字,大约阅读时间需要 4 分钟。

2018年11月11日 星期日 近段时间打算在FPGA——quartus上实现千兆以太网

一、对网卡的重新认识: 网卡工作在ISO/OSI的最后两层:物理层和数据链路层。 1、物理层:定义了数据传送与接收所需要的电光信号、线路状态、数据编码和电路等等,并向数据链路层设备提供标准接口。物理层的芯片称之为PHY芯片 、----------------------------------------------------------------、 2、数据链路层:提供寻址,数据帧的构建,数据差错检查,传送控制,向网络层提供标准的数据接口等功能。以太网卡中数据链路层的芯片称之为MAC控制器。 很多网卡的这两个部分是做到一起的,他们之间的关系是PCI总线接MAC总线,MAC控制器接PHY,PHY又接网线(当然并非完全直接接上,中间又一些电容等)

3、PHY和MAC之间又是如何传送数据和相互沟通的呢?

IEEE定义了标准的MII/GigaMII(Media Independed Interface)。MII传递了网络的所有数据和数据的控制,而MAC对PHY的工作状态的确定和对PHY的控制则是使用SMI(serial Management Interface)界面通过读写PHY的寄存器来完成的。MAC通过SMI总线不断的读取PHY的状态寄存器以得知目前PHY的状态

上述3.大致了解留个印象即可,暂时还不具体明白

也就是说,我们不用管PHY层,因为PHY层次,使用RTL8211EG这款芯片来实现的,我们只用管数据链路层,数据链路层的MAC控制芯片,便是我们的FPGA芯片。

*----------------------------------------------------------------- RTL8211EG 支持MDI/MDX自适应,各种速度自适应,maser/slave自适应RTL8211EG上电会检测一些特定的IO的电平状态,从而确定自己的工作模式

补充:此CRC为自定义添加,只针对UDP帧头到数据末尾,不对其他数据位进行校验,也就是说,只有数据到了UDP帧头才开始计算CRC,到数据末尾结束,并将结果(32bit=4Byte)附在末尾。二、PHY芯片之RTL8211EG芯片介绍

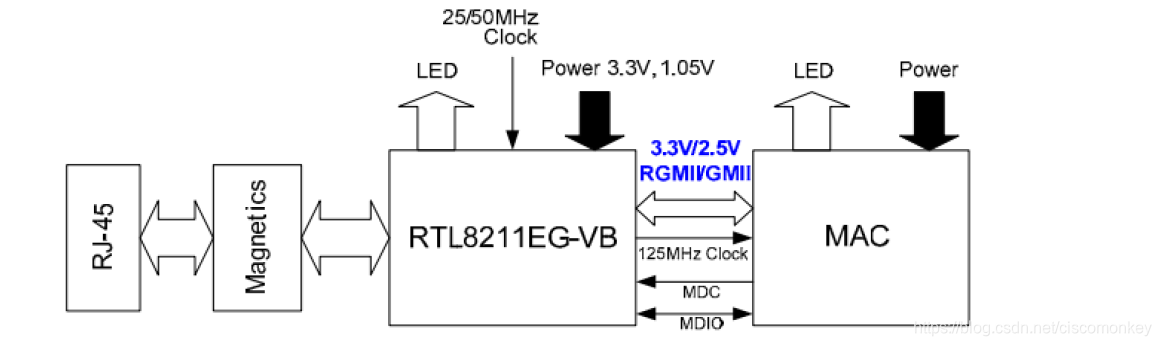

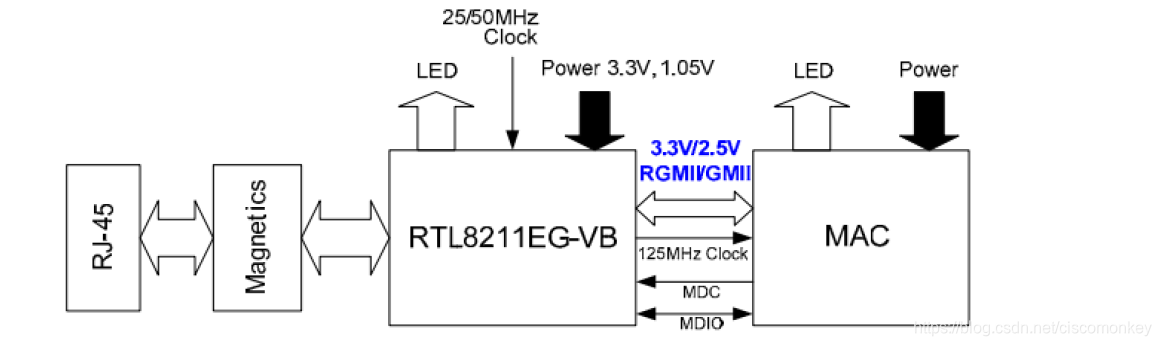

RTL8211EG是由Realtek公司推出的千兆网PHY芯片,RTL8211EG芯片作为千兆网PHY芯片,它与MAC层的接口可通过RGMII(Reduced Gigabit Media Independent interface:简化的千兆介质无关接口)和GMLL(Gigabit Media Independent interface千兆介质无关接口)进行通信,

时钟部分就不多说了,图上很清新,可以通过过MDC/MDIO管理接口来配置或读取PHY芯片内部的寄存器。由于RTL8211EG芯片只提供PHY层功能,不包括MAC、UDP、TCP等功能,所以我们需要私用FPGA来实现这些功能来完成数据通信。

下图来自datasheet上图是该芯片的管脚

--------------------------------下次继续转载地址:https://blog.csdn.net/ciscomonkey/article/details/83997412 如侵犯您的版权,请留言回复原文章的地址,我们会给您删除此文章,给您带来不便请您谅解!

发表评论

最新留言

网站不错 人气很旺了 加油

[***.192.178.218]2024年04月03日 22时43分55秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

VMware 虚拟化编程(9) — VMware 虚拟机的快照

2019-04-27

VMware 虚拟化编程(10) — VMware 数据块修改跟踪技术 CBT

2019-04-27

VMware 虚拟化编程(11) — VMware 虚拟机的全量备份与增量备份方案

2019-04-27

VMware 虚拟化编程(12) — VixDiskLib Sample 程序使用

2019-04-27

VMware 虚拟化编程(13) — VMware 虚拟机的备份方案设计

2019-04-27

VMware 虚拟化编程(14) — VDDK 的高级传输模式详解

2019-04-27

VMware 虚拟化编程(15) — VMware 虚拟机的恢复方案设计

2019-04-27

Socket 网络编程实践经验

2019-04-27

消息队列在分布式系统中的应用

2019-04-27

计算机网络基础 — Linux 虚拟交换机

2019-04-27

基于 Linux Bridge 的 Neutron 多平面网络实现原理

2019-04-27

OpenvSwitch — Overview

2019-04-27

启用 SR-IOV 解决 Neutron 网络 I/O 性能瓶颈

2019-04-27

CentOS7 通过 YUM 升级 VIM8

2019-04-27

Cinder 架构分析、高可用部署与核心功能解析

2019-04-27

我非要捅穿这 Neutron(一)网络实现模型篇

2019-04-27

我非要捅穿这 Neutron(二)上层资源模型篇

2019-04-27

KVM 开启嵌套虚拟化

2019-04-27