verilog基础篇RAM IP核的使用

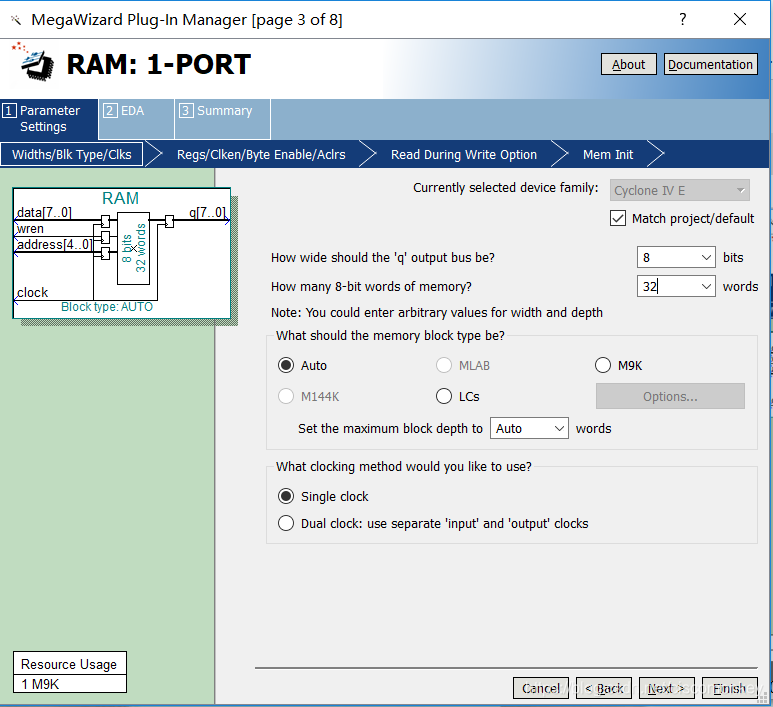

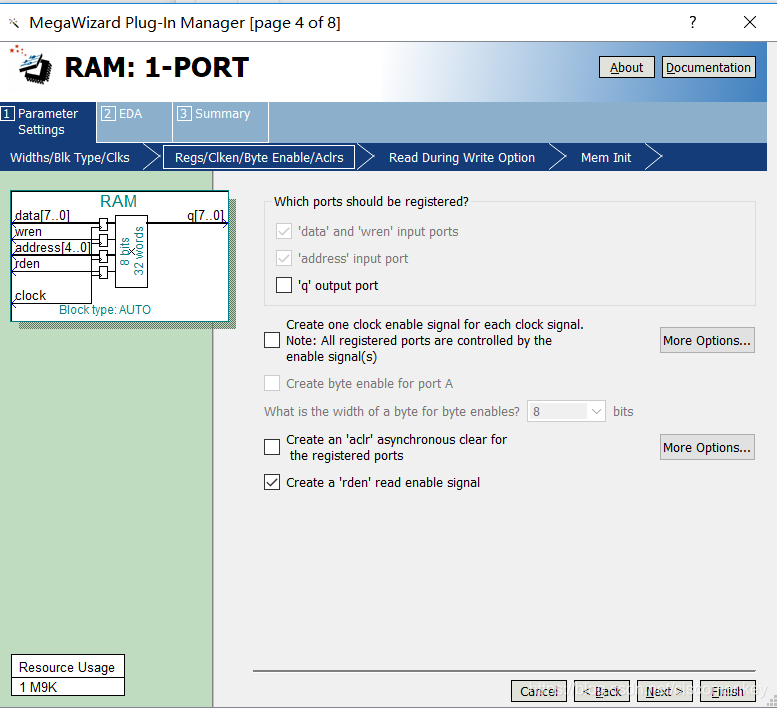

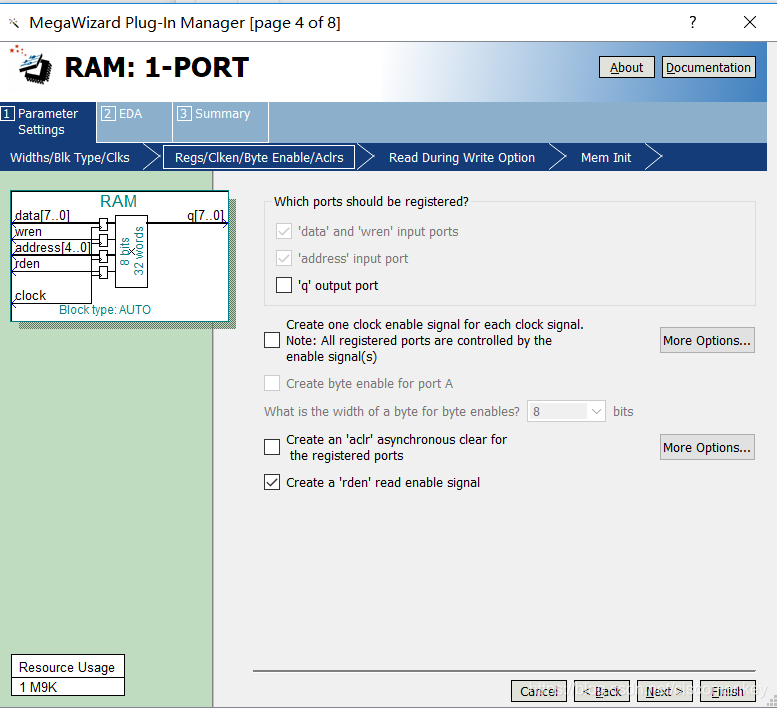

在该页面中,我们去掉了q output port(去掉输出寄存器),并且添加了一个rden读使能信号,所谓rden读使能信号就是,当该信号为高电平时,我们才可以读取RAM IP核中的数据。 其余的页面我们使用默认设置即可,不要忘记勾选inst初始化模板文件。

在该页面中,我们去掉了q output port(去掉输出寄存器),并且添加了一个rden读使能信号,所谓rden读使能信号就是,当该信号为高电平时,我们才可以读取RAM IP核中的数据。 其余的页面我们使用默认设置即可,不要忘记勾选inst初始化模板文件。

发布日期:2021-05-15 10:42:49

浏览次数:15

分类:技术文章

本文共 2126 字,大约阅读时间需要 7 分钟。

在该页面中,我们去掉了q output port(去掉输出寄存器),并且添加了一个rden读使能信号,所谓rden读使能信号就是,当该信号为高电平时,我们才可以读取RAM IP核中的数据。 其余的页面我们使用默认设置即可,不要忘记勾选inst初始化模板文件。

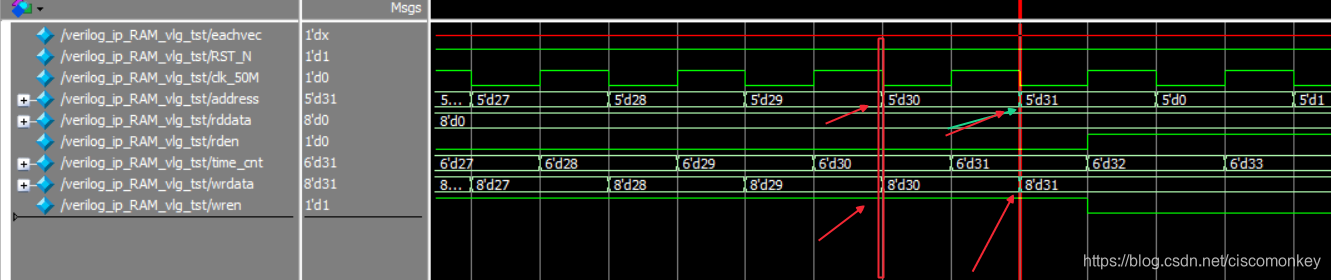

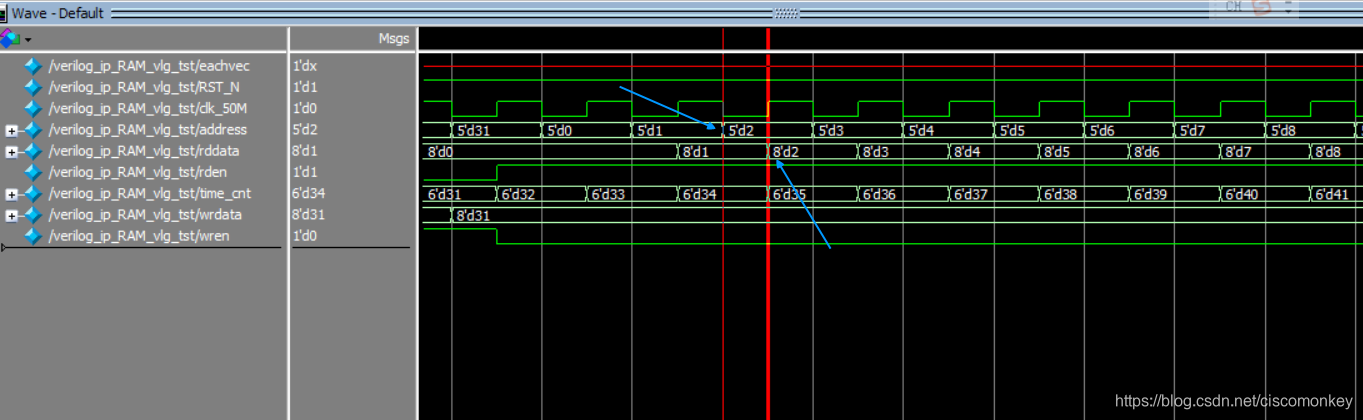

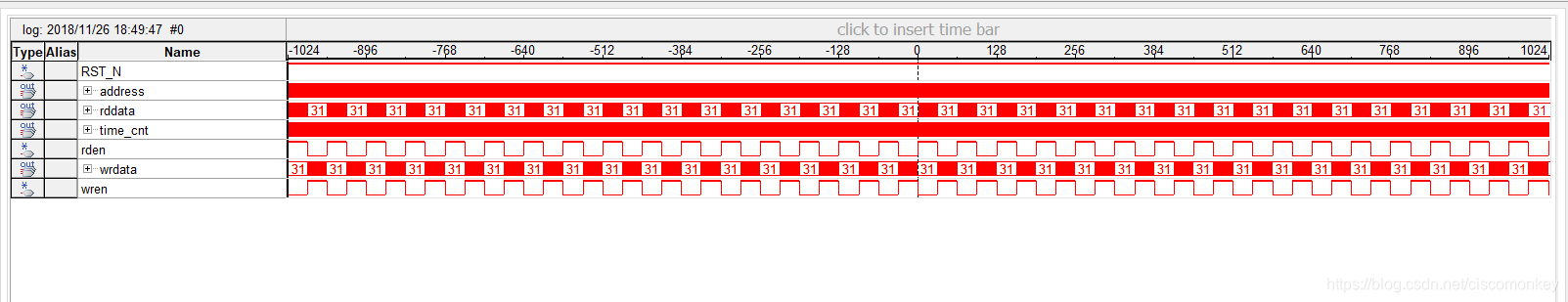

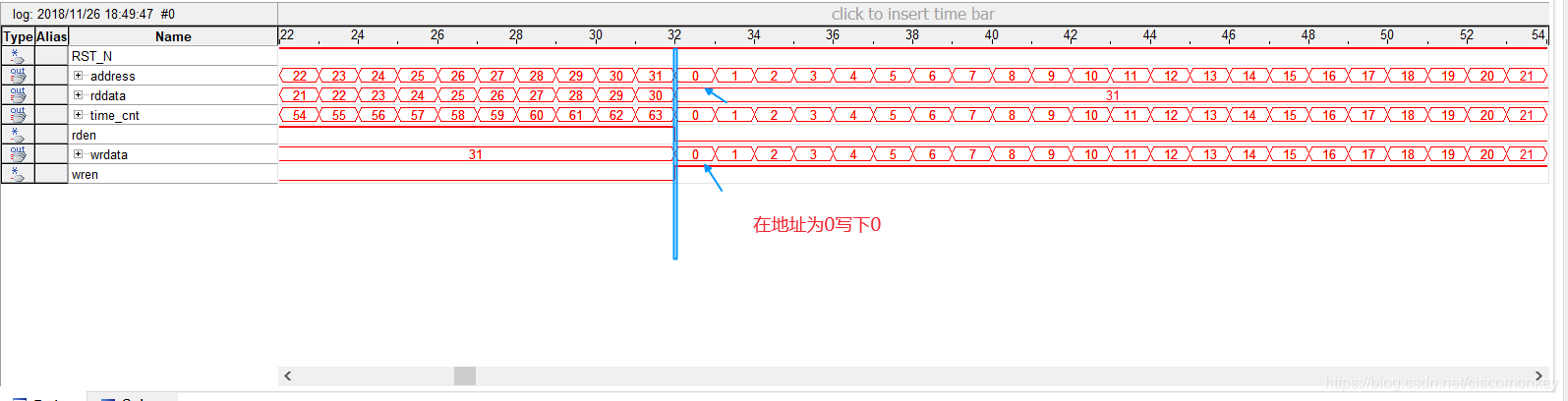

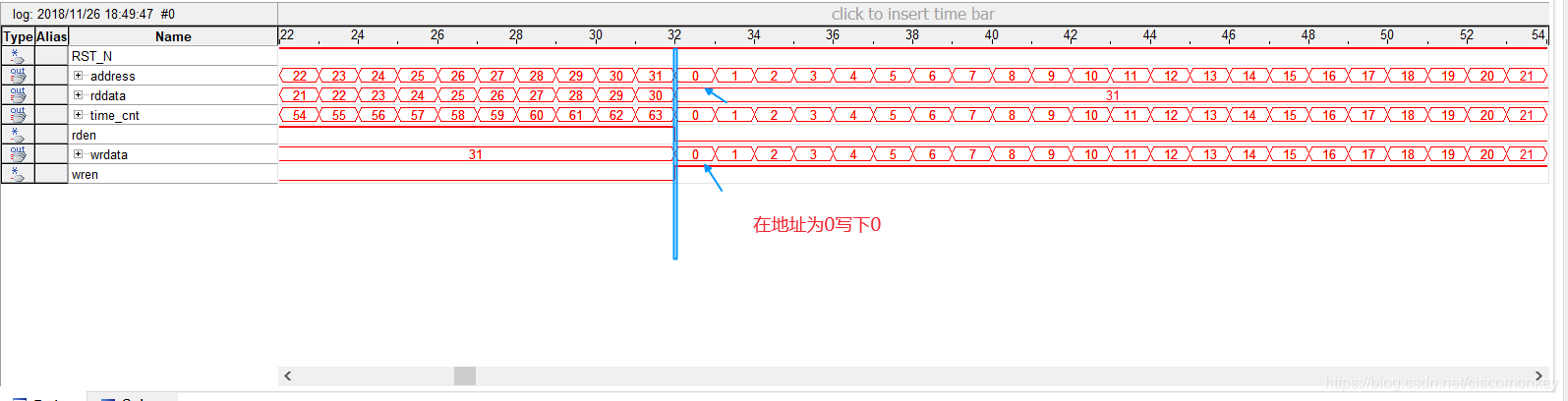

在该页面中,我们去掉了q output port(去掉输出寄存器),并且添加了一个rden读使能信号,所谓rden读使能信号就是,当该信号为高电平时,我们才可以读取RAM IP核中的数据。 其余的页面我们使用默认设置即可,不要忘记勾选inst初始化模板文件。 //该代码主要实现了先往RAM IP核中的0-31地址写入0-31数据, //每个地址对应一个数据,比如0地址对应0数据,1地址对应1数据,以此类推 //写完了32个数据之后,我们在将RAM IP核中的0-31地址中的数据读出 //当写数据时,我们需要将写使能信号拉高,当读数据时,我们需要将读使能信号拉高

//该代码主要实现了先往RAM IP核中的0-31地址写入0-31数据,

//每个地址对应一个数据,比如0地址对应0数据,1地址对应1数据,以此类推 //写完了32个数据之后,我们在将RAM IP核中的0-31地址中的数据读出 //当写数据时,我们需要将写使能信号拉高,当读数据时,我们需要将读使能信号拉高module verilog_ip_RAM(input clk_50M,input RST_N,/*RAM端口*/output reg [4:0] address, //RAM的地址端口output reg [7:0] wrdata, //RAM的写数据端口output [7:0] rddata, //RAM的读数据端口output reg [5:0] time_cnt, //计数器output wren, //RAM的写使能端口output rden //RAM的读使能端口);//计数器reg [5:0] time_cnt_n;//time_cnt的下一个状态 //RAM的地址端口reg [4:0] address_n; //address的下一个状态 //RAM的写数据端口reg [7:0] wrdata_n; //wrdata的下一个状态//时序逻辑电路,用来给time_cnt寄存器赋值always @ (posedge clk_50M or negedge RST_N)beginif(!RST_N) time_cnt<=1'b0;else time_cnt<=time_cnt_n;end/*组合电路*/always @ (*)begin if(time_cnt==6'd63) time_cnt_n=0; else time_cnt_n=time_cnt+1;end/*时序电路,用来给address寄存器赋值*/always @ (negedge clk_50M or negedge RST_N)begin if(!RST_N) address<=1'b0; else address<=address_n;end/*组合电路,用来生成RAM地址*/always @ (*)begin if(address==5'd31) address_n=1'b0; else address_n=address+1'b1;end/*组合电路,根据计数器用来生成RAM写使能*/assign wren = (time_cnt>=1'b0&&time_cnt<=5'd31)?1'b1:1'b0;/*时序电路,用来给wrdata寄存器赋值*/always @ (negedge clk_50M or negedge RST_N)begin if(!RST_N) wrdata<=1'b0; else wrdata<=wrdata_n; end/*组合电路,根据计数器用来生成写入RAM的数据*/always @ (*)begin if(time_cnt>=1'b0&&time_cnt<=5'd31) wrdata_n=time_cnt; else wrdata_n=wrdata;end/*组合电路,根据计数器用来生成RAM读使能*/assign rden =(time_cnt>=6'd32&&time_cnt<=6'd63)?1'b1:1'b0;/*RAM IP核模块*/RAM RAM_inst ( .address ( address ), //RAM的地址端口 .clock ( clk_50M ), //时钟端口 .data ( wrdata ),//RAM的写数据端口 .rden ( rden ), //RAM的读使能端口 .wren ( wren ), //RAM的写使能端口 .q ( rddata ) //RAM的读数据端口 ); endmodule

转载地址:https://blog.csdn.net/ciscomonkey/article/details/84549195 如侵犯您的版权,请留言回复原文章的地址,我们会给您删除此文章,给您带来不便请您谅解!

发表评论

最新留言

哈哈,博客排版真的漂亮呢~

[***.90.31.176]2024年04月07日 21时56分29秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

Spring 核心 之 IOC

2019-04-26

一起来学MySQL—事务的隔离级别

2019-04-26

直连线和交叉线的区别

2019-04-26

数据库视频—使用.Net访问SQL Server

2019-04-26

数据库视频—总结

2019-04-26

简单工厂模式和策略模式的比较

2019-04-26

简单工厂、工厂方法、抽象工厂模式

2019-04-26

单例模式

2019-04-26

组合模式

2019-04-26

三层架构

2019-04-26

委托与事件(浅度分析)—委托

2019-04-26

委托与事件(浅度分析)—事件

2019-04-26

.NET框架

2021-06-29

VB.NET入门

2021-06-29

七层登录

2021-06-29

Polar bear and air-conditioner

2021-06-29

不加注解引起的500错误

2021-06-29

PB使用专用接口连接SQL Server

2021-06-29

PB中创建需要带参数查询的DataWindow

2021-06-29

idea如何设置自动换行

2021-06-29