vivado SOC——hello word(上)建立SOC系统

点击ok

点击ok

发布日期:2021-05-15 10:42:51

浏览次数:13

分类:技术文章

本文共 571 字,大约阅读时间需要 1 分钟。

引言

本节为了熟悉vivado的SOC使用,由于我也是开始学,所以请一起学的人点评指点。软件:vivado 2016.4

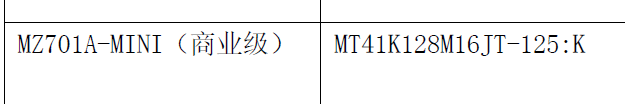

板子:米联客701A mini-

开发板介绍

-

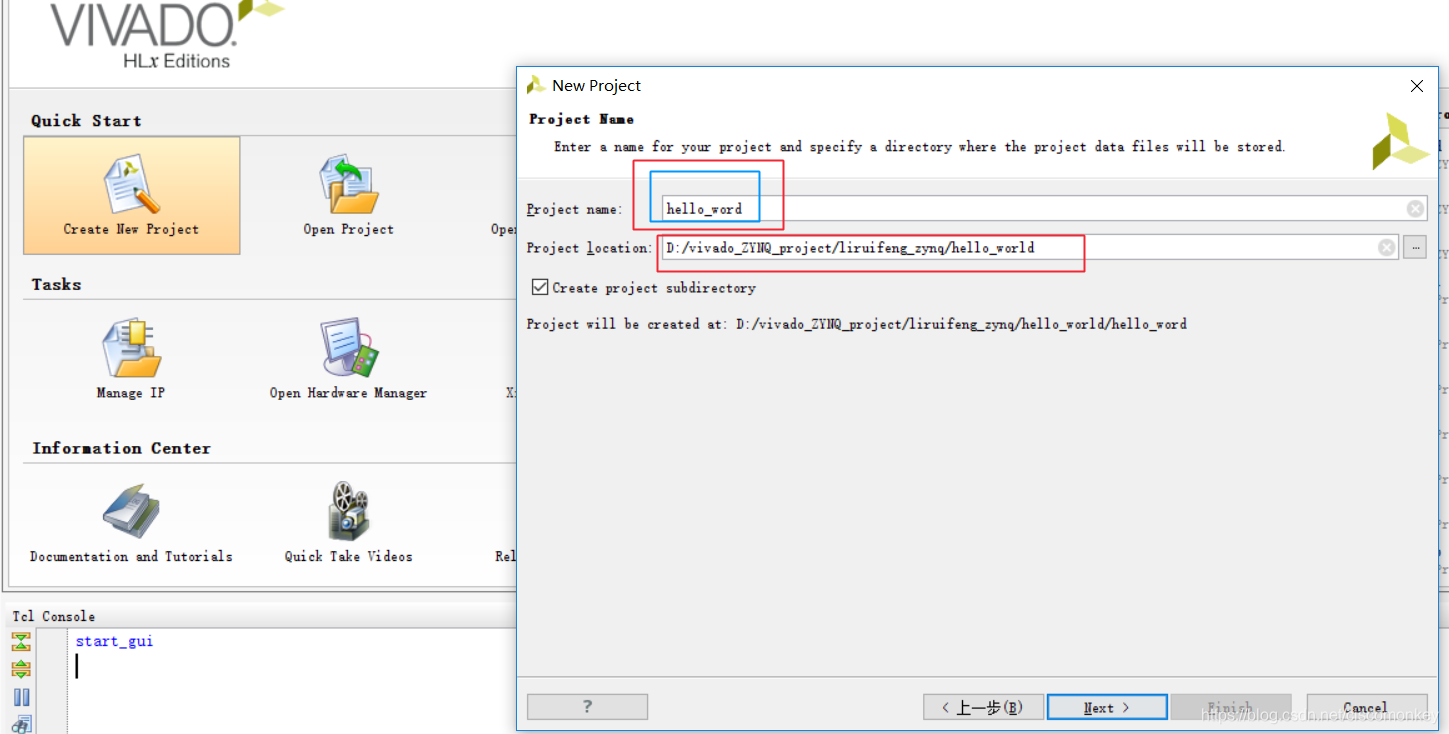

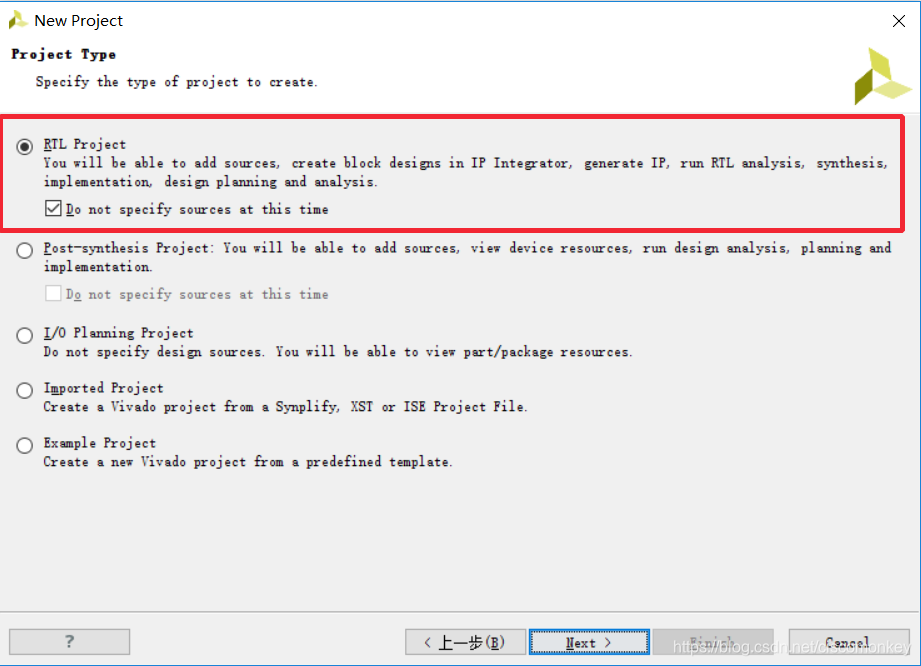

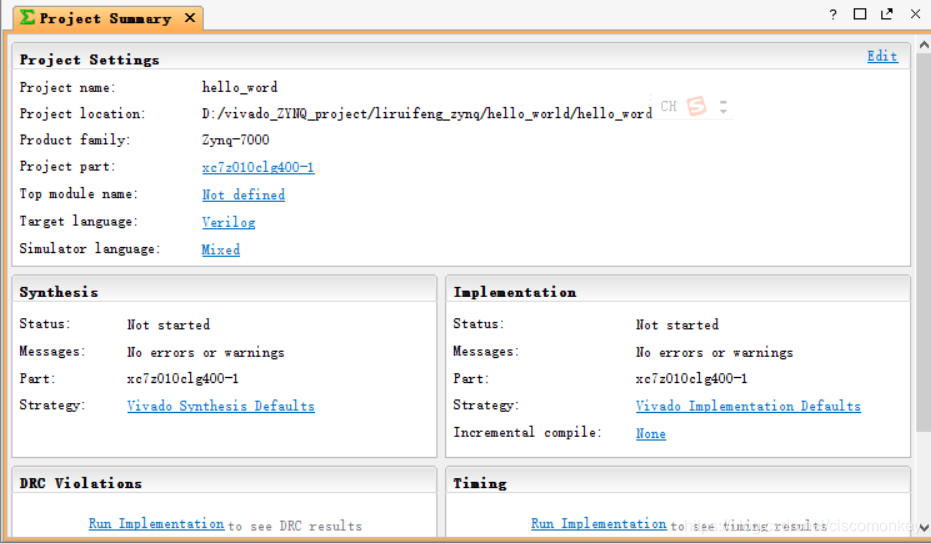

创建工程

-

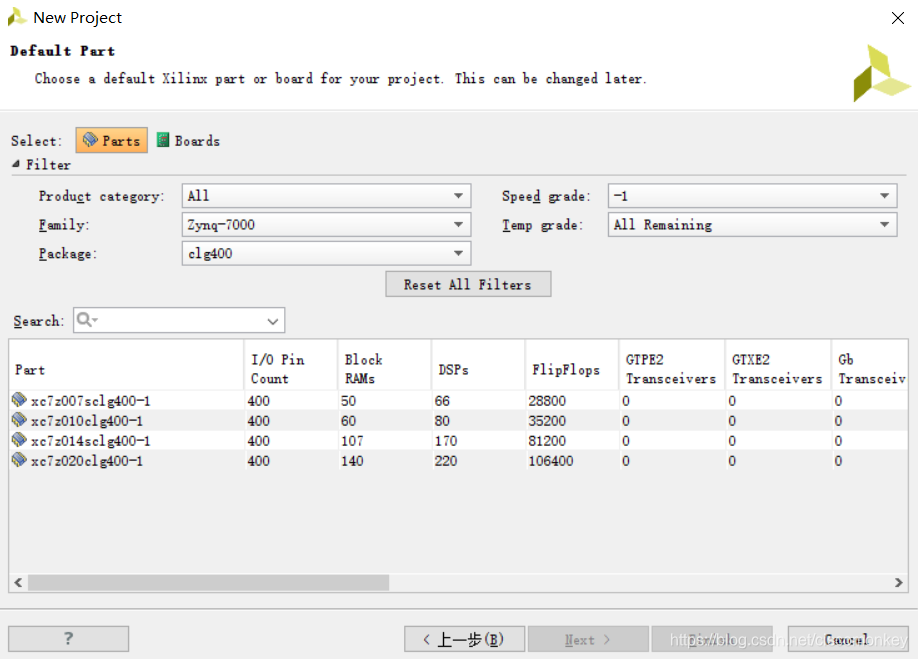

选择ZYNQ的型号和封装格式

这一块可以查看原理图获知,然后点击next,finish即可 -

下面开始搭建SOC(也就是搭建我们的硬件系统)

创建最小系统,

给最小系统起一个名字,这里我们起名叫system。

-

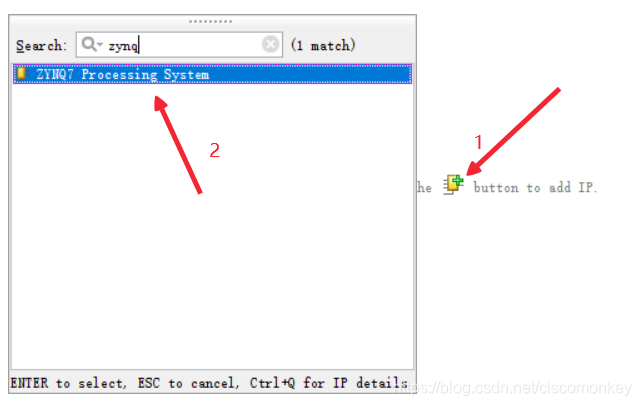

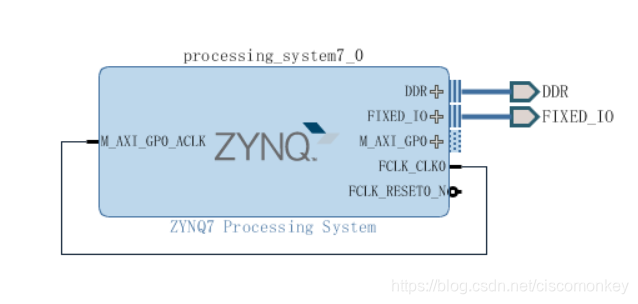

添加ZYNQ的处理系统IP

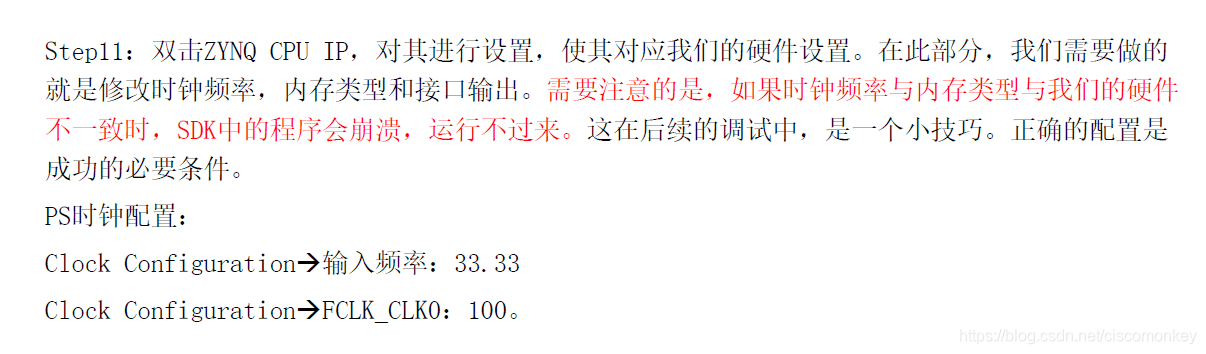

- 设置ZYNQ处理系统

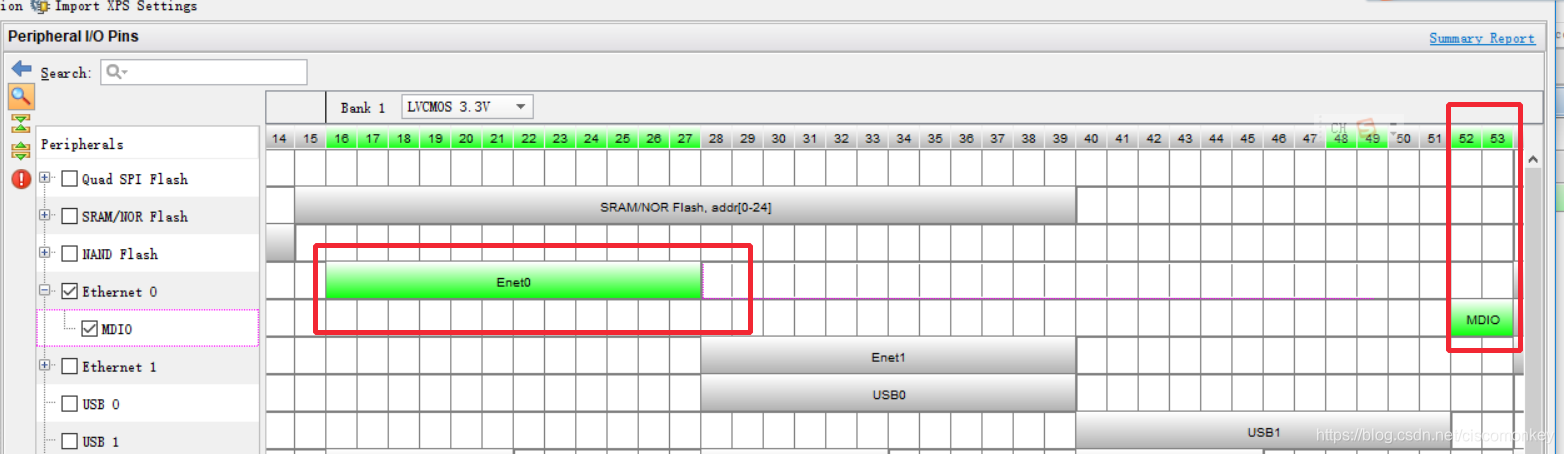

IO设置

我们的核心板上具有一个uart,我们需要通过uart来传输hello world的信息

所以我们的ZYNQ最小系统需要一个uart。

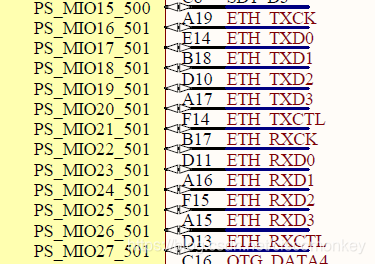

勾选uart1,uart1对应的48脚和49脚,必须对应我们的硬件原理图,我们的硬件也是48脚和49脚

由于后续我们要测试网口,所以我们把网口也连上

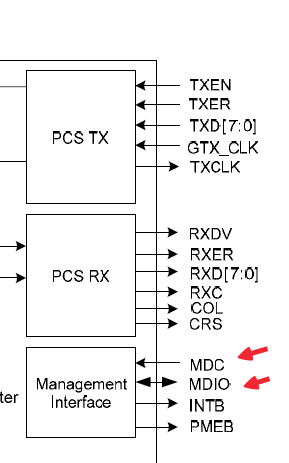

下图是PHY芯片的管脚,52 53为配置管脚链接PHY

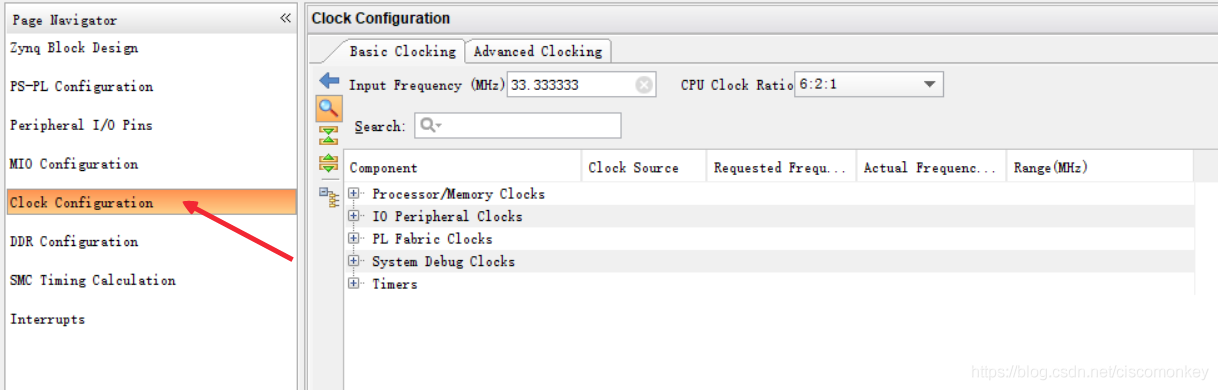

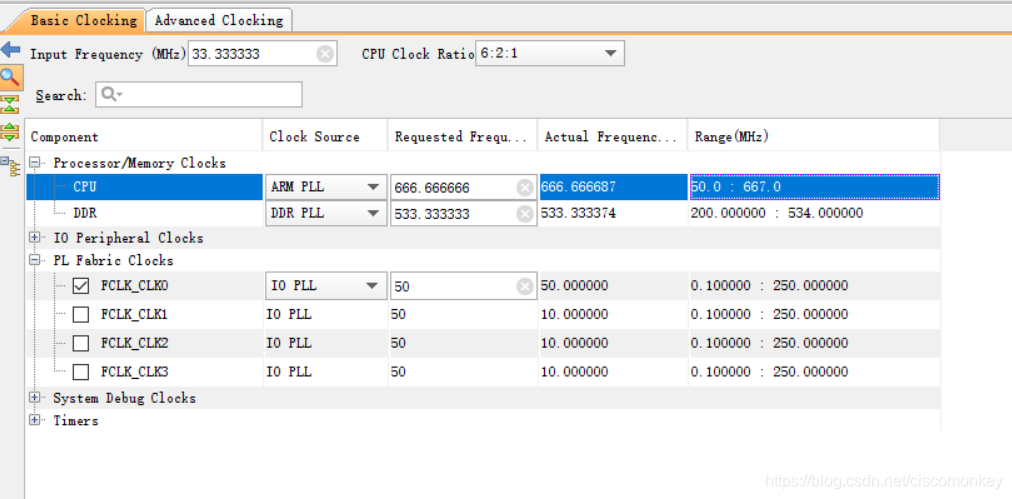

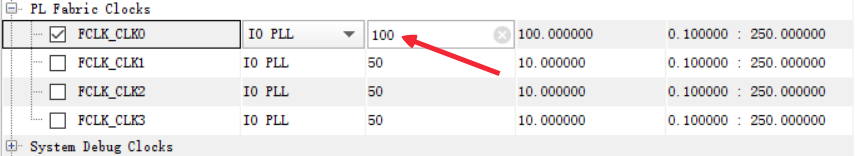

- 下面配置系统时钟PS时钟和PL时钟

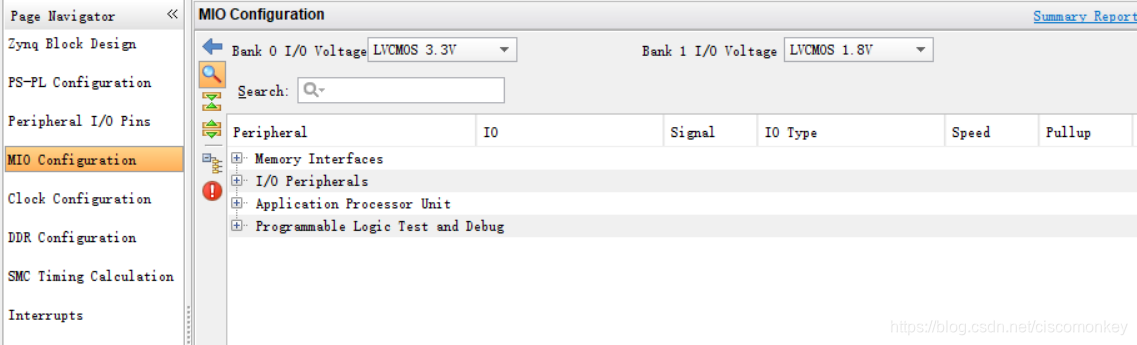

- 电压设置

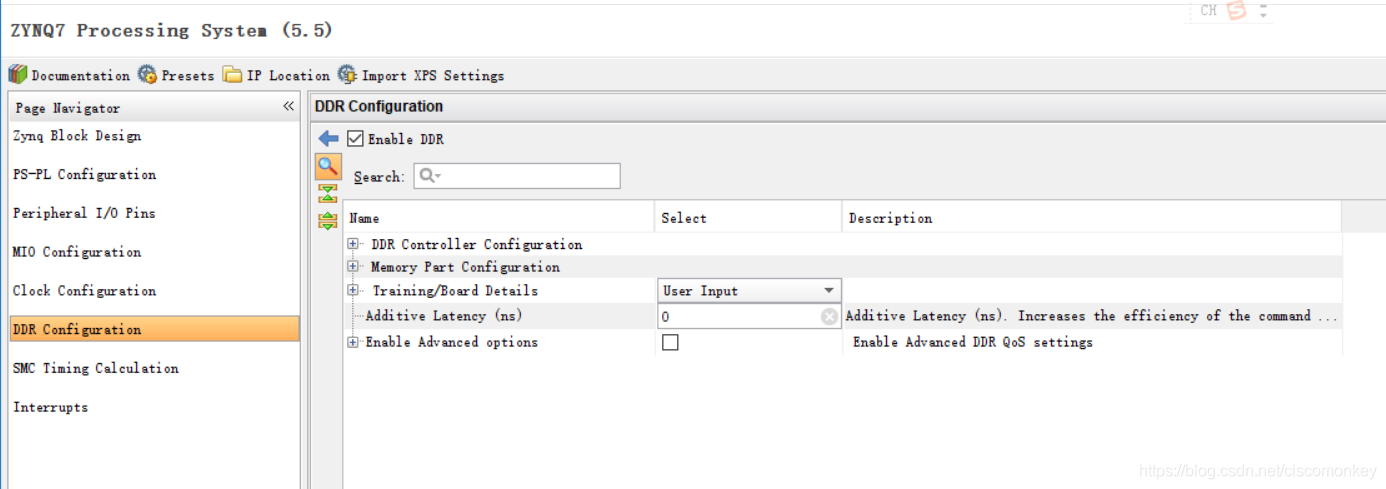

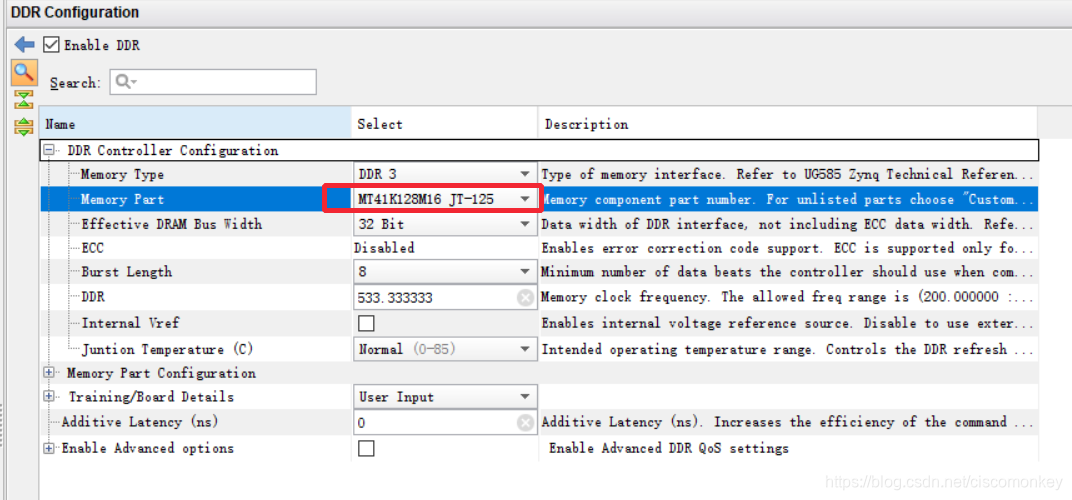

- 设置DDR

128乘以16=256M(2048除以8)

点击ok

点击ok -

运行

点击自动运行,他会帮我们把这些外设链接好

我们把这条线也连接上

-

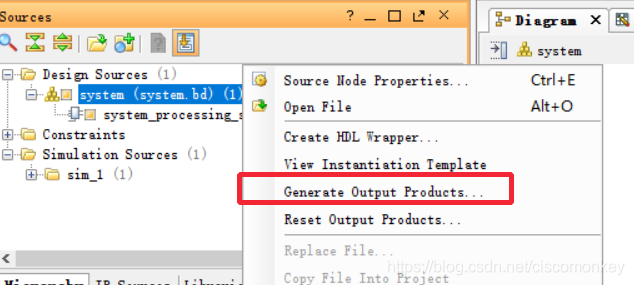

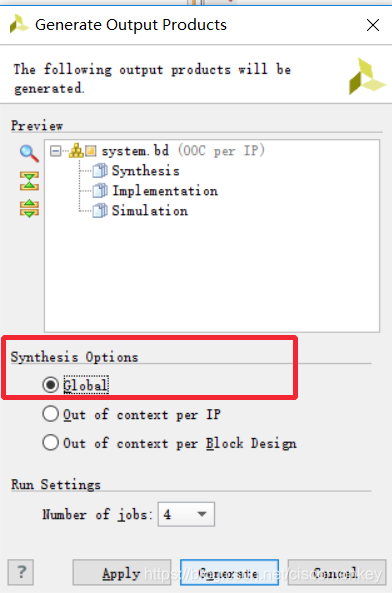

generate outpt product

产生硬件模型 -

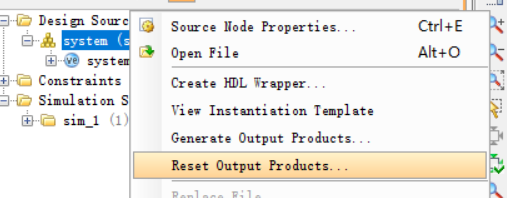

如果系统发生错误

清除之前产生的文件 -

产生HDL wrapper

这是一个顶层文件 然后就可以产生bitstrem

转载地址:https://blog.csdn.net/ciscomonkey/article/details/84554898 如侵犯您的版权,请留言回复原文章的地址,我们会给您删除此文章,给您带来不便请您谅解!

发表评论

最新留言

能坚持,总会有不一样的收获!

[***.219.124.196]2024年04月04日 15时33分53秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

[转] 用python编写控制网络设备的自动化脚本3:启动

2019-04-26

扩展Python控制台实现中文反馈信息

2019-04-26

扩展Python控制台实现中文反馈信息之二-正则替换

2019-04-26

在PyPI测试平台发布Python包

2019-04-26

中文代码示例之Electron桌面应用开发初体验

2019-04-26

中文代码示例之NW.js桌面应用开发初体验

2019-04-26

为《 两周自制脚本语言 》添加中文测试代码

2019-04-26

将《 两周自制脚本语言 》测试中使用的接口中文化

2019-04-26

5分钟入门LingaScript-尝鲜中文版TypeScript

2019-04-26

重拾《 两周自制脚本语言 》- 支持中文标识符

2019-04-26

Java实现文本编辑时基于拼音输入的补全原型

2019-04-26

从立创EDA,Gratipay看中文编程开发环境和推广运营的一个趋势

2019-04-26

中文代码之Django官方入门:建立模型

2019-04-26

Python实现推流直播

2019-04-26

你不得不了解的卷积神经网络发展史

2019-04-26

你不得不了解的机器学习知识

2019-04-26

你不得不了解的深度学习知识(一)

2019-04-26