FPGA学习笔记Project基于Quartus Prime和ModelSim任务task的使用

发布日期:2021-07-01 03:12:26

浏览次数:2

分类:技术文章

本文共 2404 字,大约阅读时间需要 8 分钟。

FPGA学习笔记Project基于Quartus Prime和ModelSim任务task的使用

一、Verilog HDL中任务:

任务的关键字是task,利用任务可以把一个大的程序模块分解成很多小的子模块,方便调试,并且能使结构清晰。

###任务(task)定义与调用的格式分别如下:task <任务名>; //注意无端口列表

端口及数据类型声明语句; 其他语句; endtask

任务调用的格式为

<任务名>(端口1,端口2,······);

任务调用时和定义时的端口变量应是一一对应的

二、实例:定义一个完成两个操作数按位与操作的任务,然后在后面的算术逻辑单元的描述中,调用该任务完成与操作。

(一) 使用Verilog HDL语言对电路进行描述

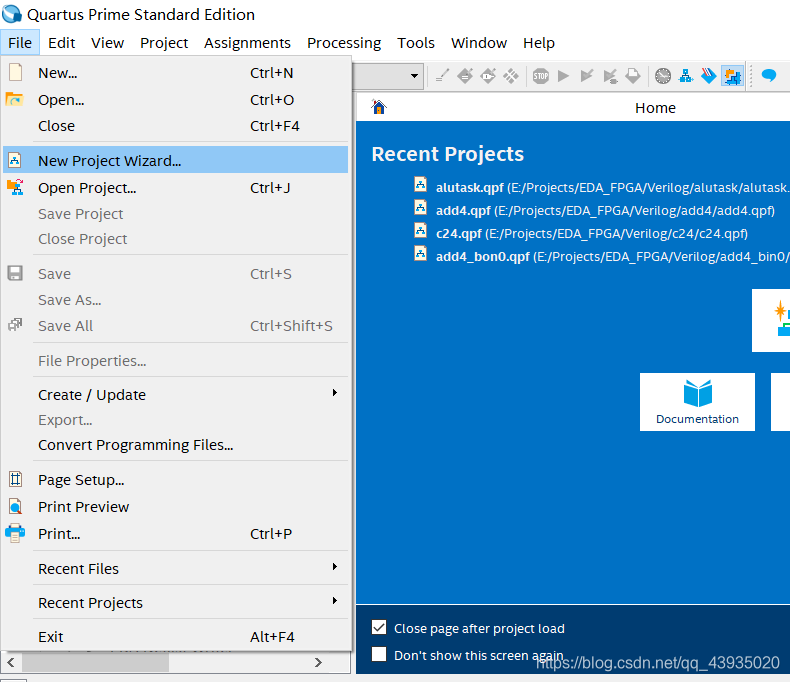

- 新建工程:File—New Project Wizard

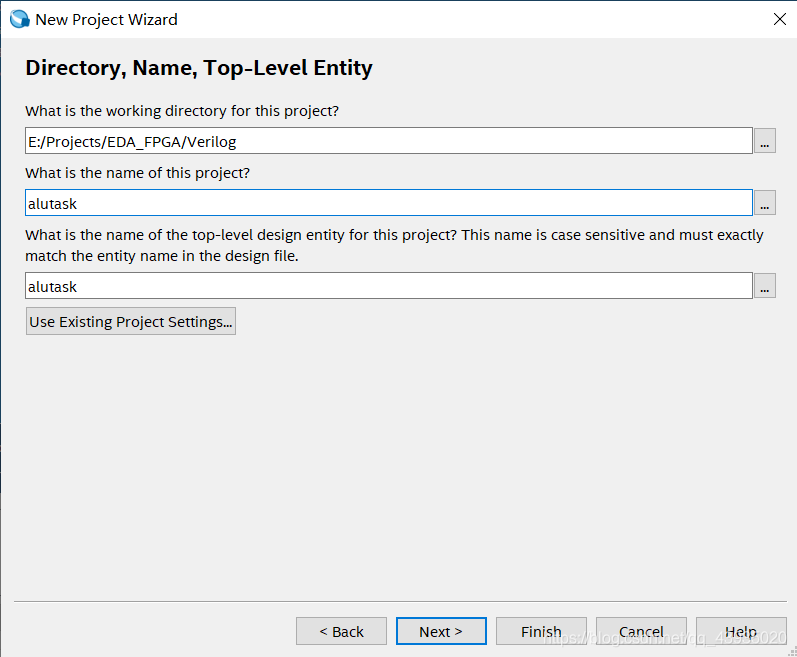

- 设置当前工作目录及工程保存路径(路径中不能有中文及空格,可使用下划线’_’);第二栏中填写工程名字;第三栏是顶层文件的实体名,一般与工程名相同。(工程名的命名一般得符合标识符的命名原则)

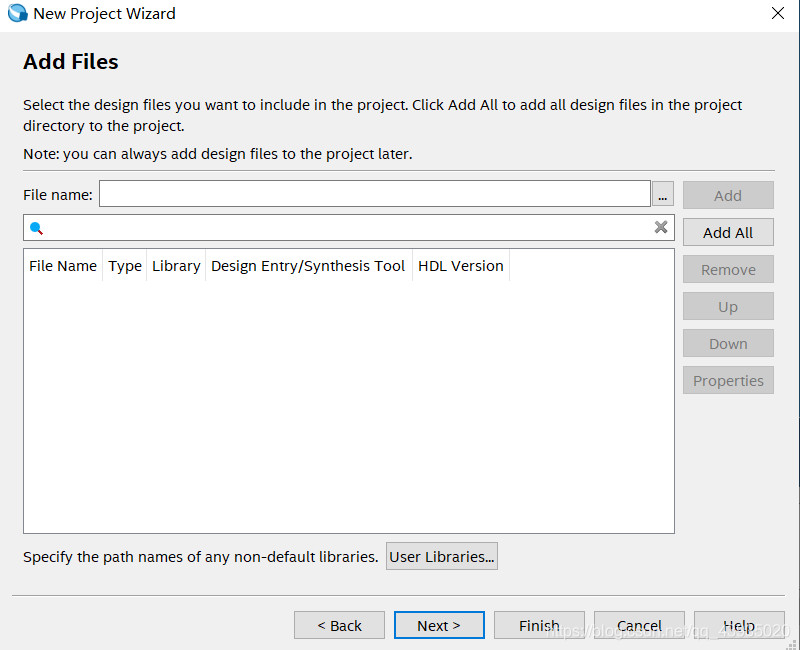

- 无相关文件需要加入,跳过即可

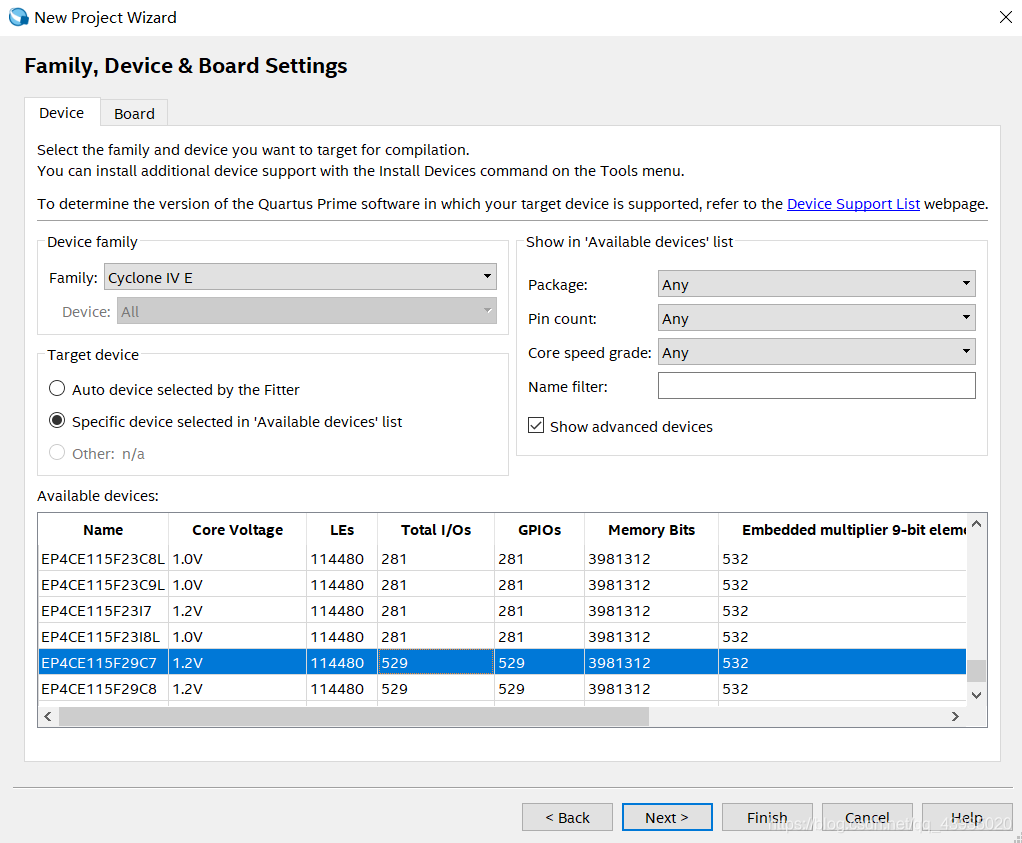

- 选择目标器件:按照实际需求选择合适的器件即可。

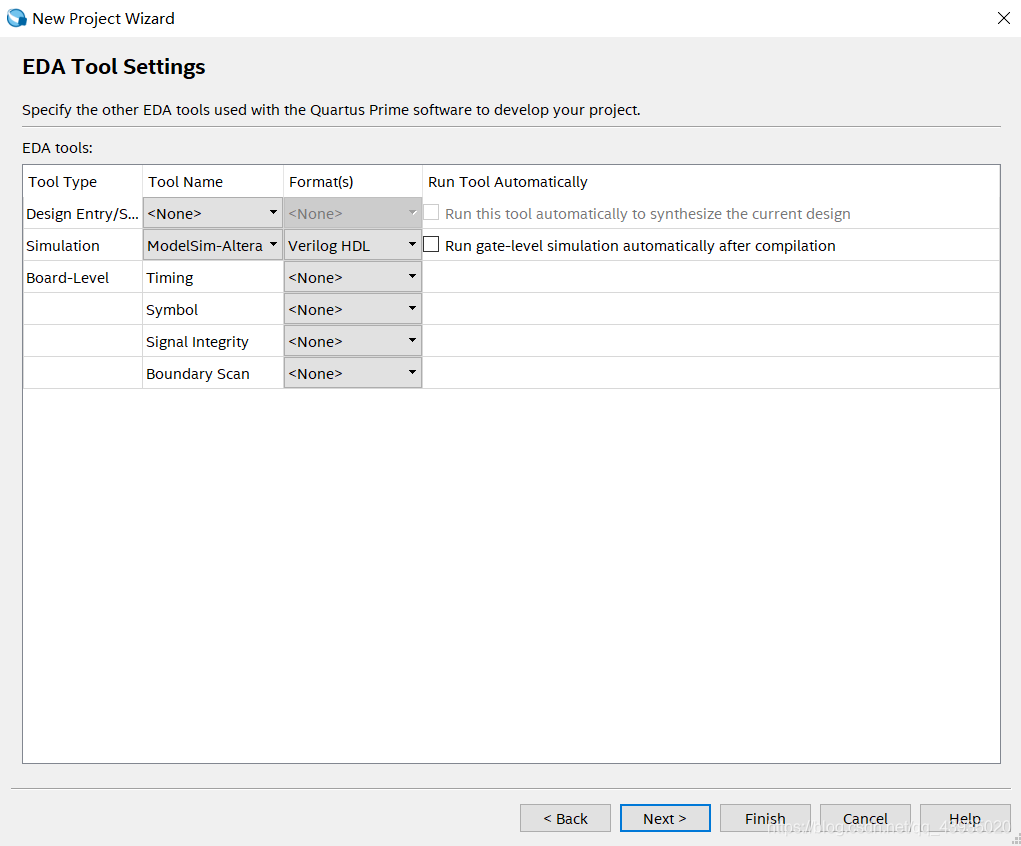

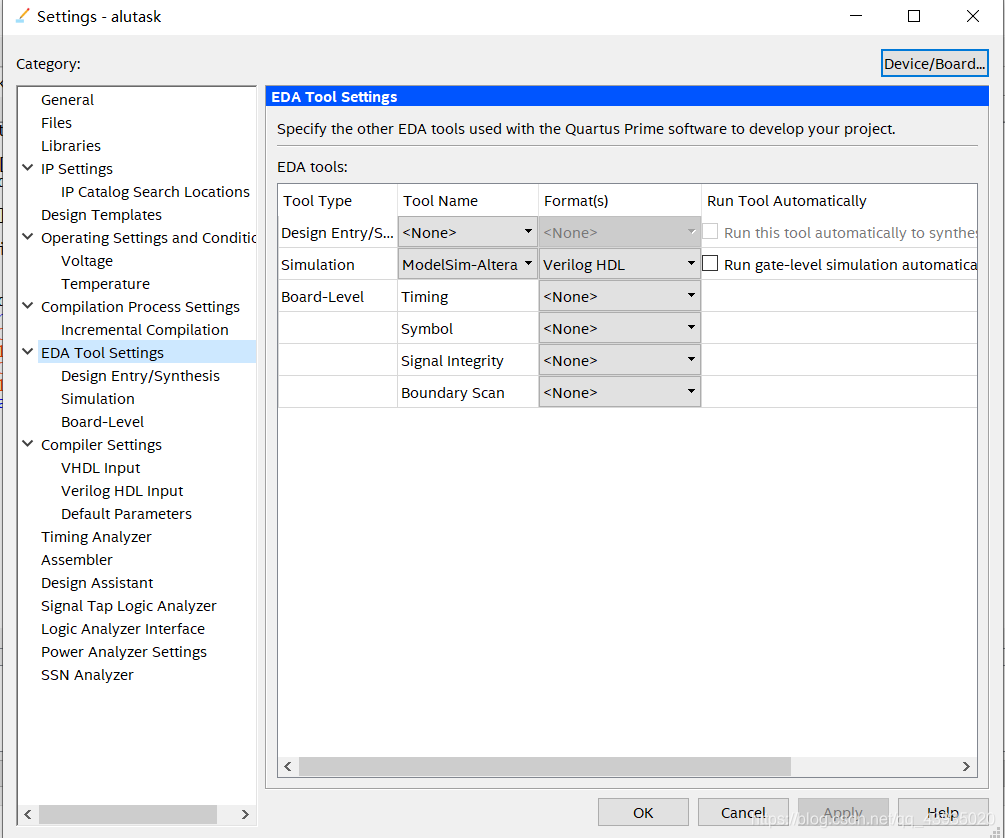

- 选择综合器和仿真器:在Simulation一行,选择ModelSim-Altera,表示选择该仿真器进行仿真;Format一栏选择Verilog HDL。

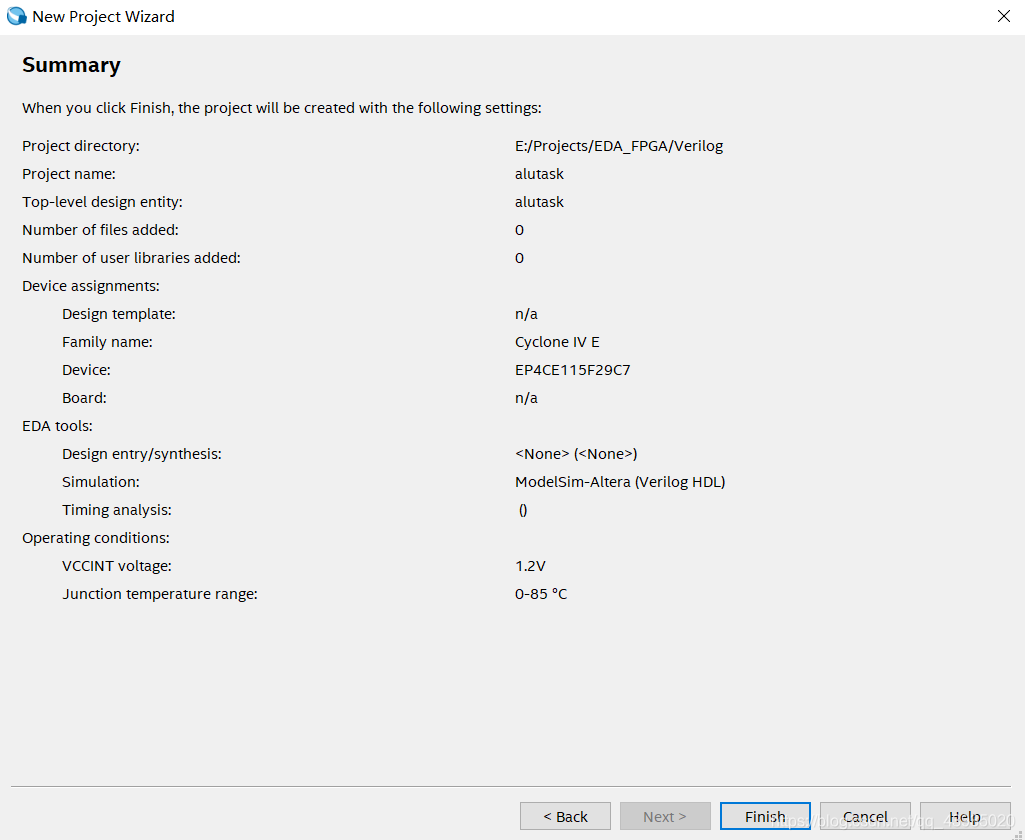

- 结束设置:出现工程信息汇总窗口(Summary)。

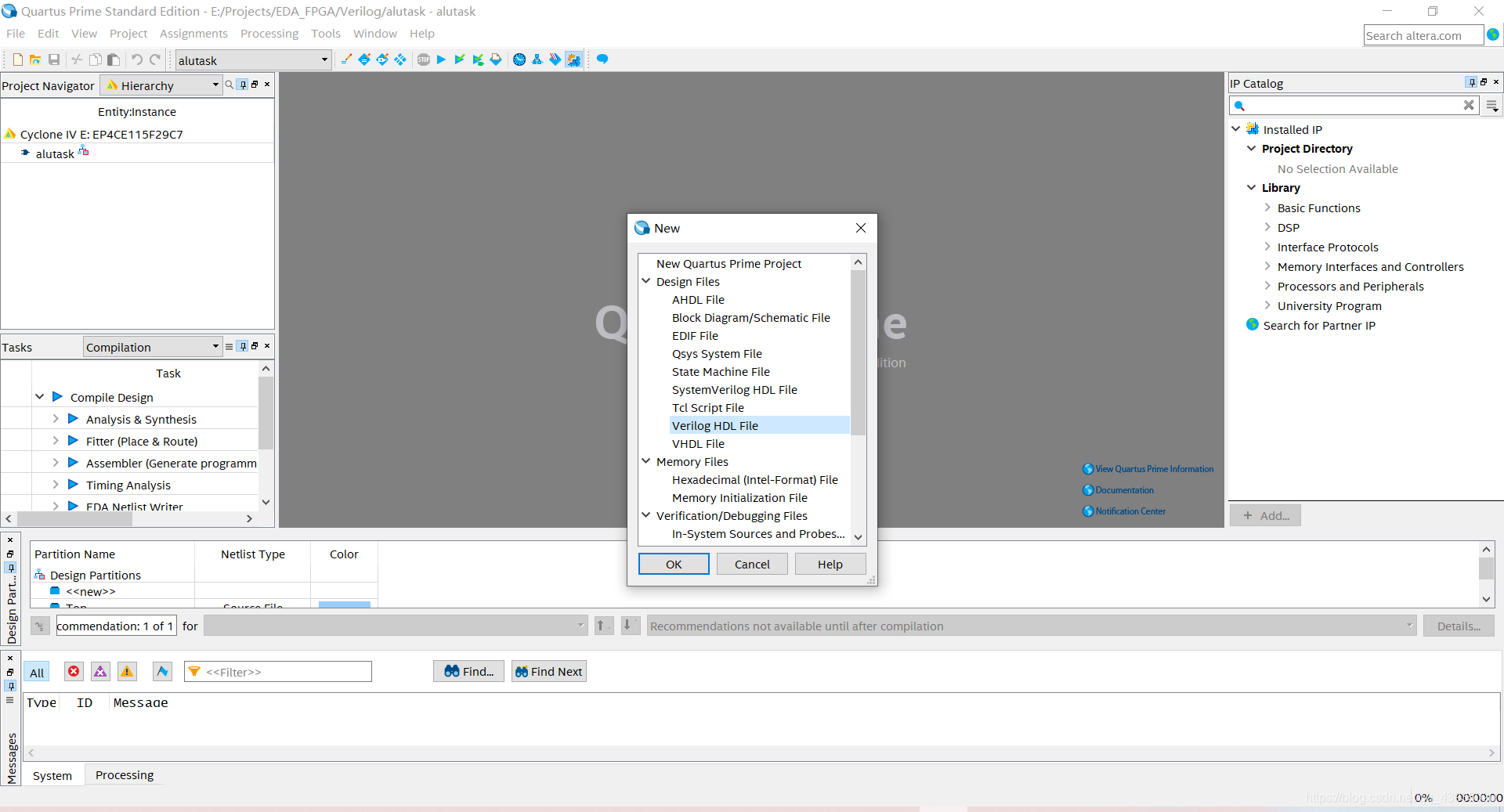

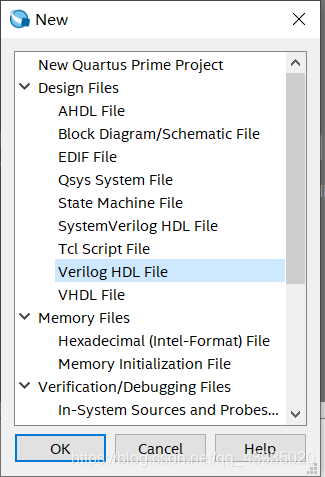

- 在当前工程内新建Verilog HDL文件:File—New—Verilog HDL File

- 输入程序

代码示例:(CSDN的Markdown编辑器好像并不支持Verilog HDL语言的高亮,借用javascript)

代码示例:(CSDN的Markdown编辑器好像并不支持Verilog HDL语言的高亮,借用javascript)

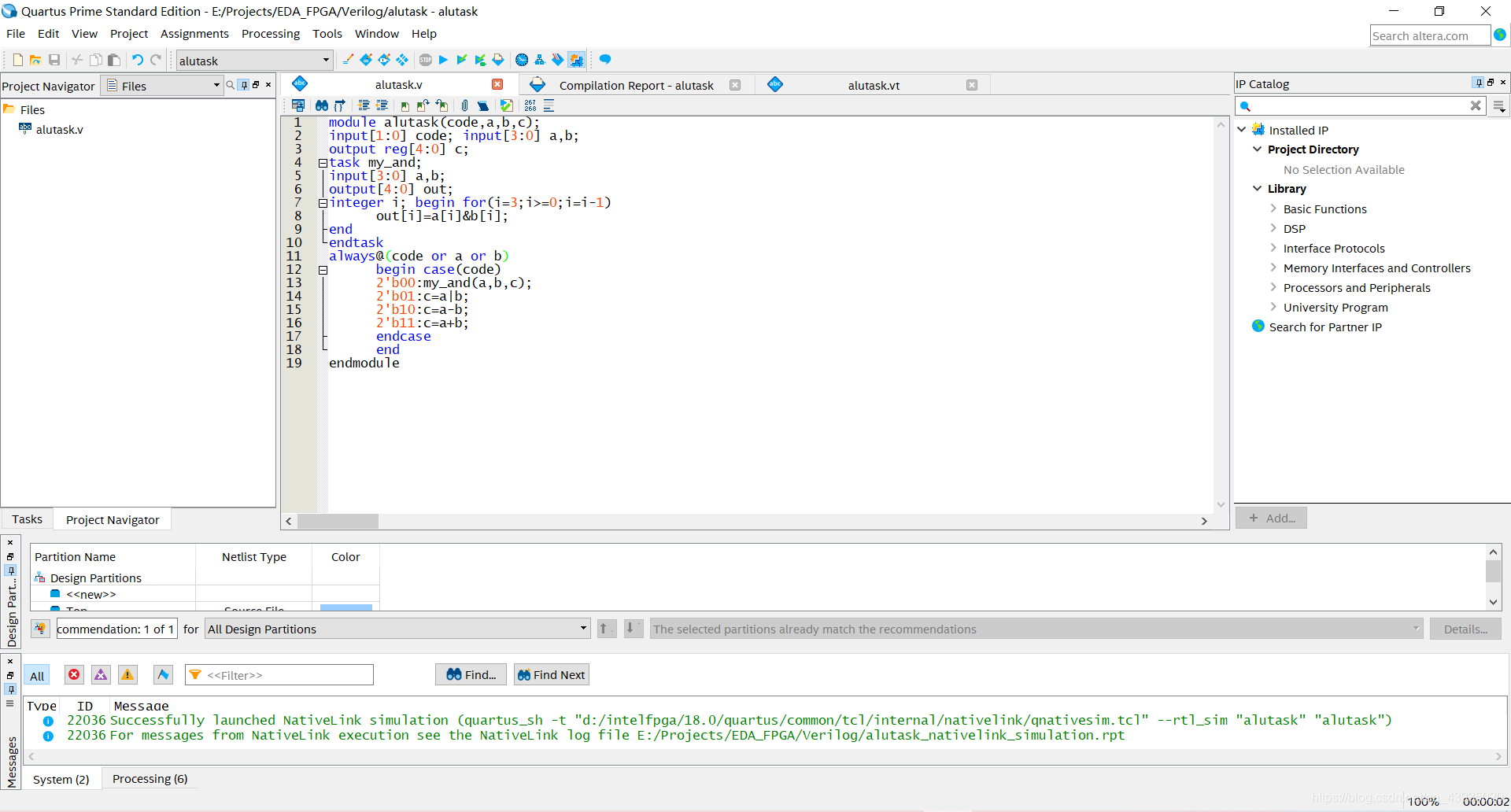

module alutask(code,a,b,c);input[1:0] code; input[3:0] a,b;output reg[4:0] c;task my_and;input[3:0] a,b;output[4:0] out;integer i; begin for(i=3;i>=0;i=i-1) out[i]=a[i]&b[i];endendtaskalways@(code or a or b) begin case(code) 2'b00:my_and(a,b,c); 2'b01:c=a|b; 2'b10:c=a-b; 2'b11:c=a+b; endcase endendmodule

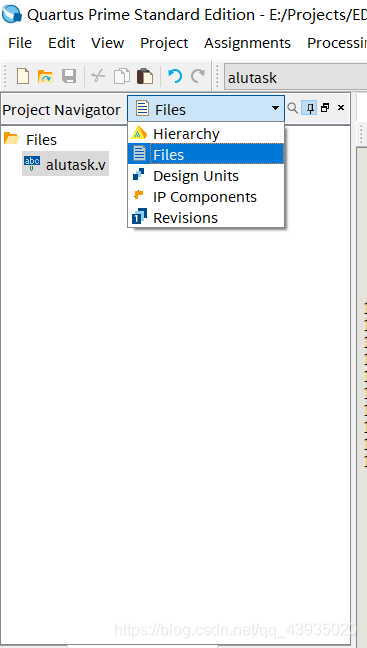

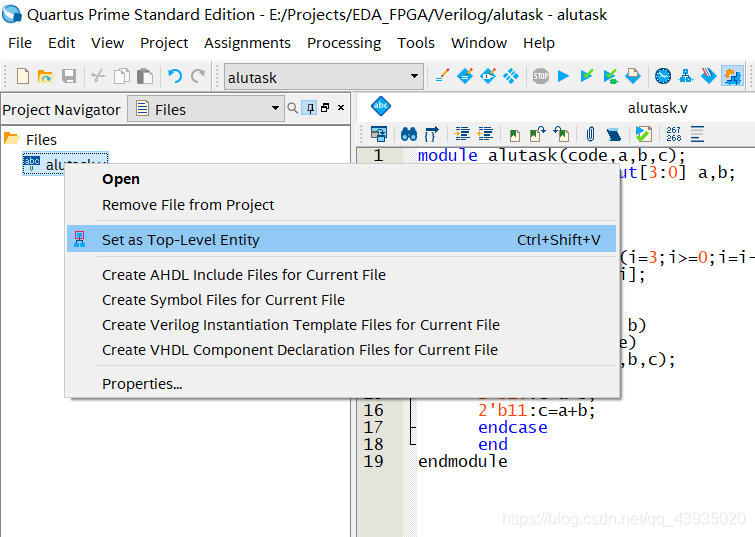

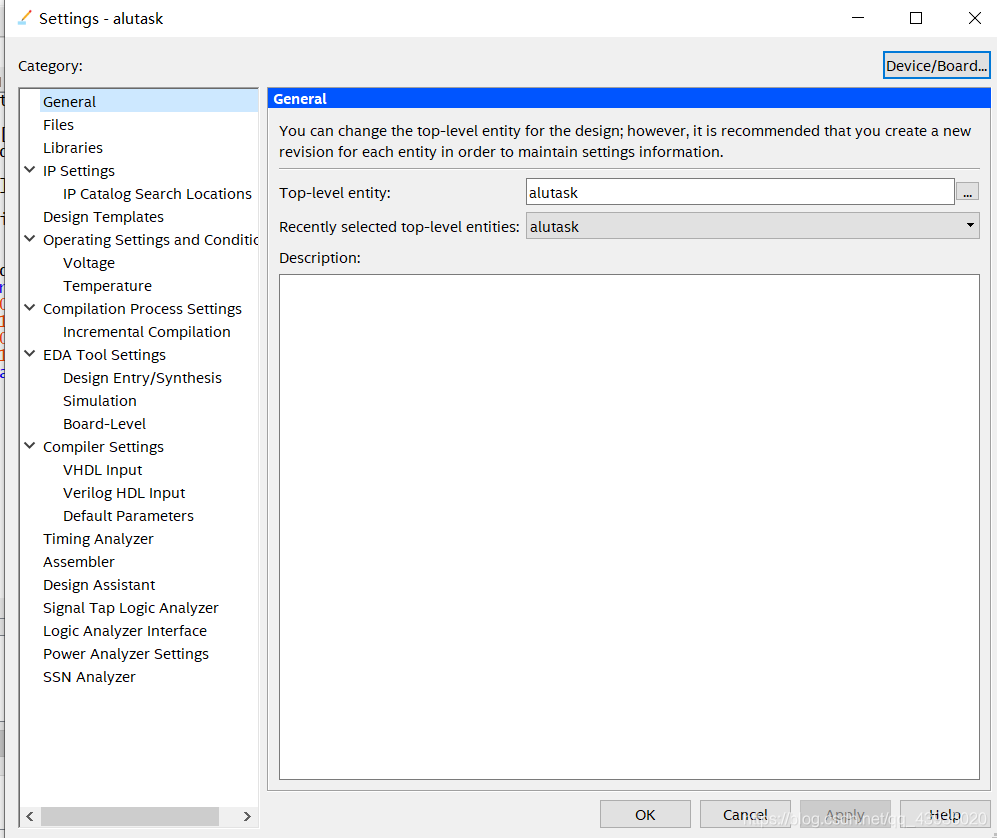

- 保存后将alutask.v文件设置为顶层实体;设置完成后可在Settings—General中查看。 -

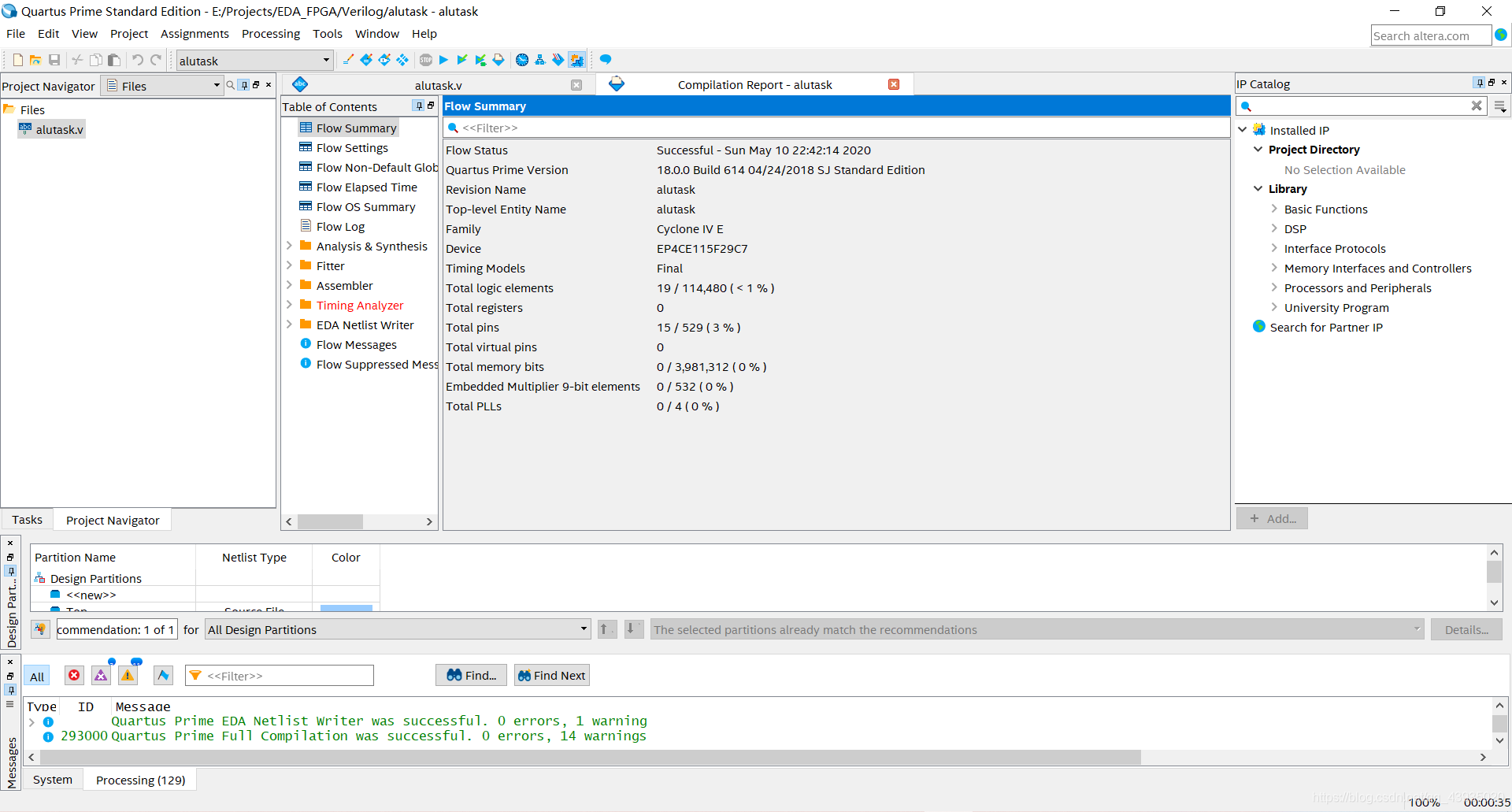

- 编译:Processing—Start Compilation;修改至零错误即可。

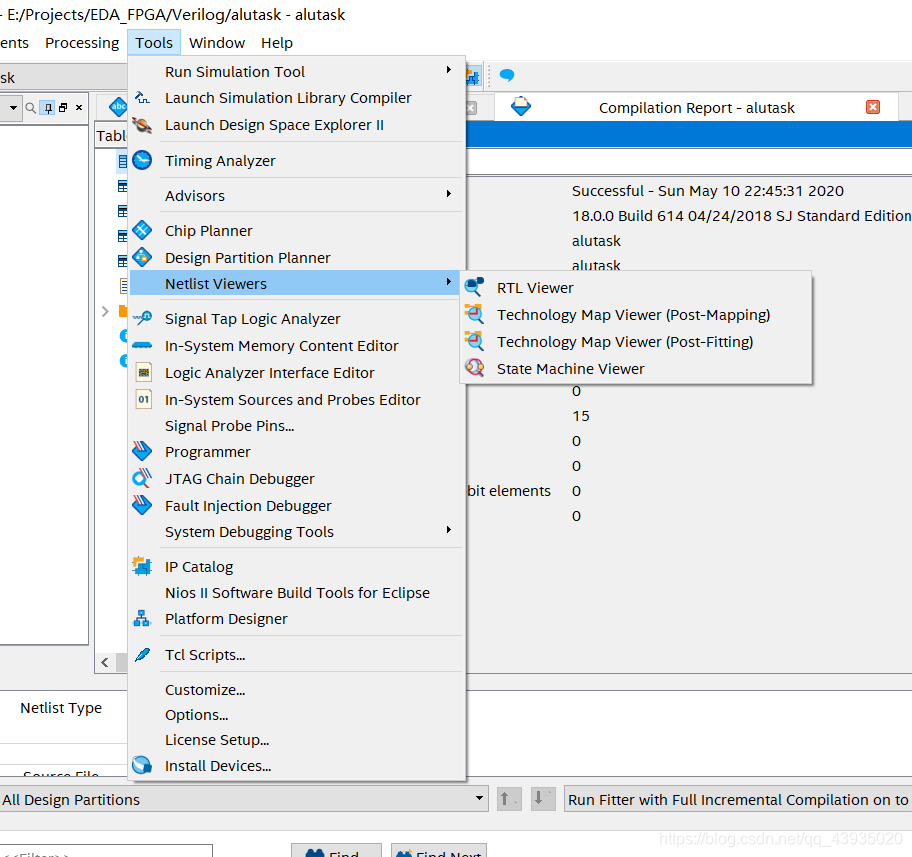

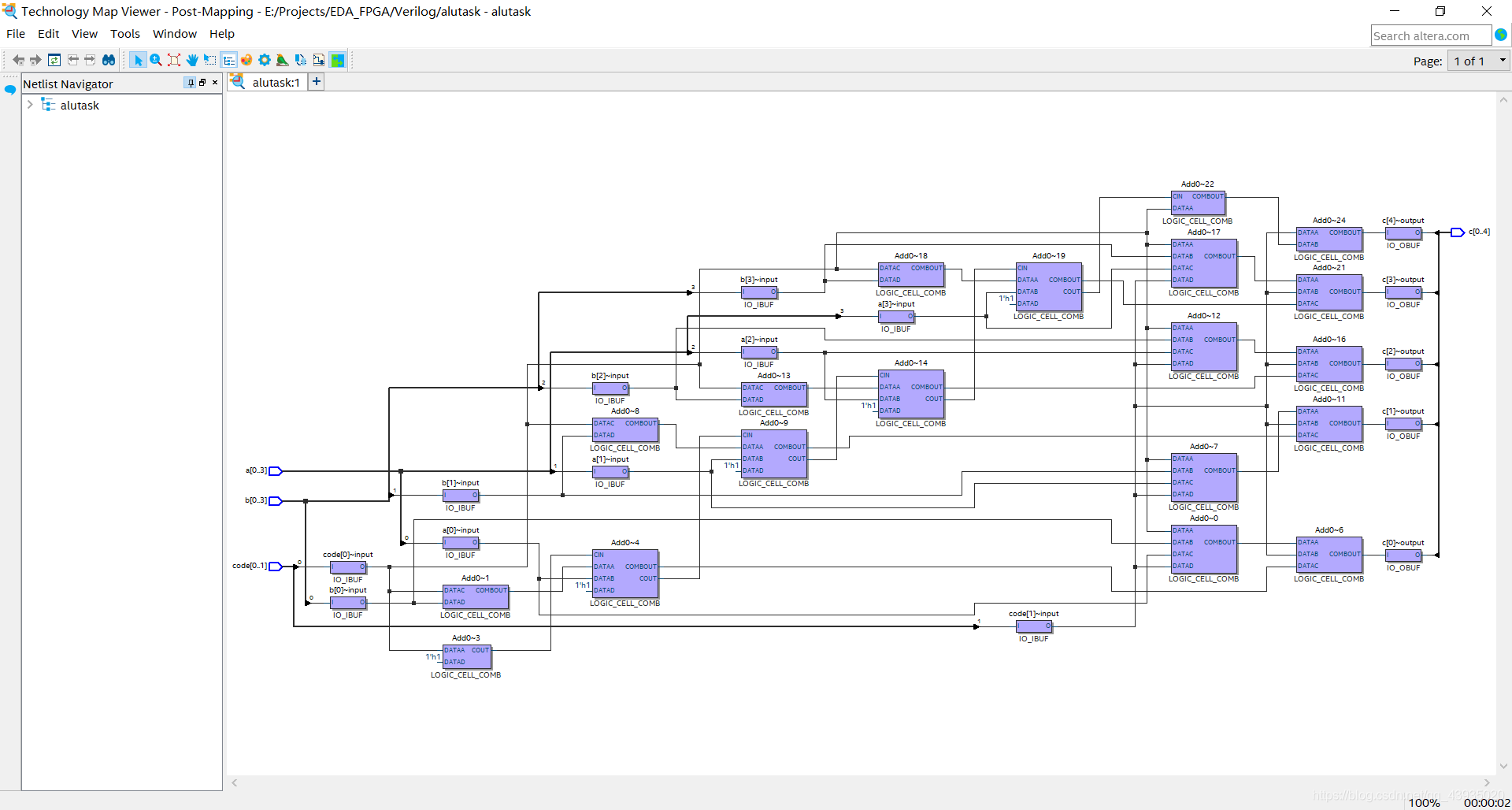

- RTL级综合及门级综合:可在Tools—Netlist Viewers中选择进行RTL级综合或者门级综合。通过综合器,能将文本描述的转化为电路网表结构,并以原理图的形式呈现出来。

(二)、使用ModelSim进行仿真

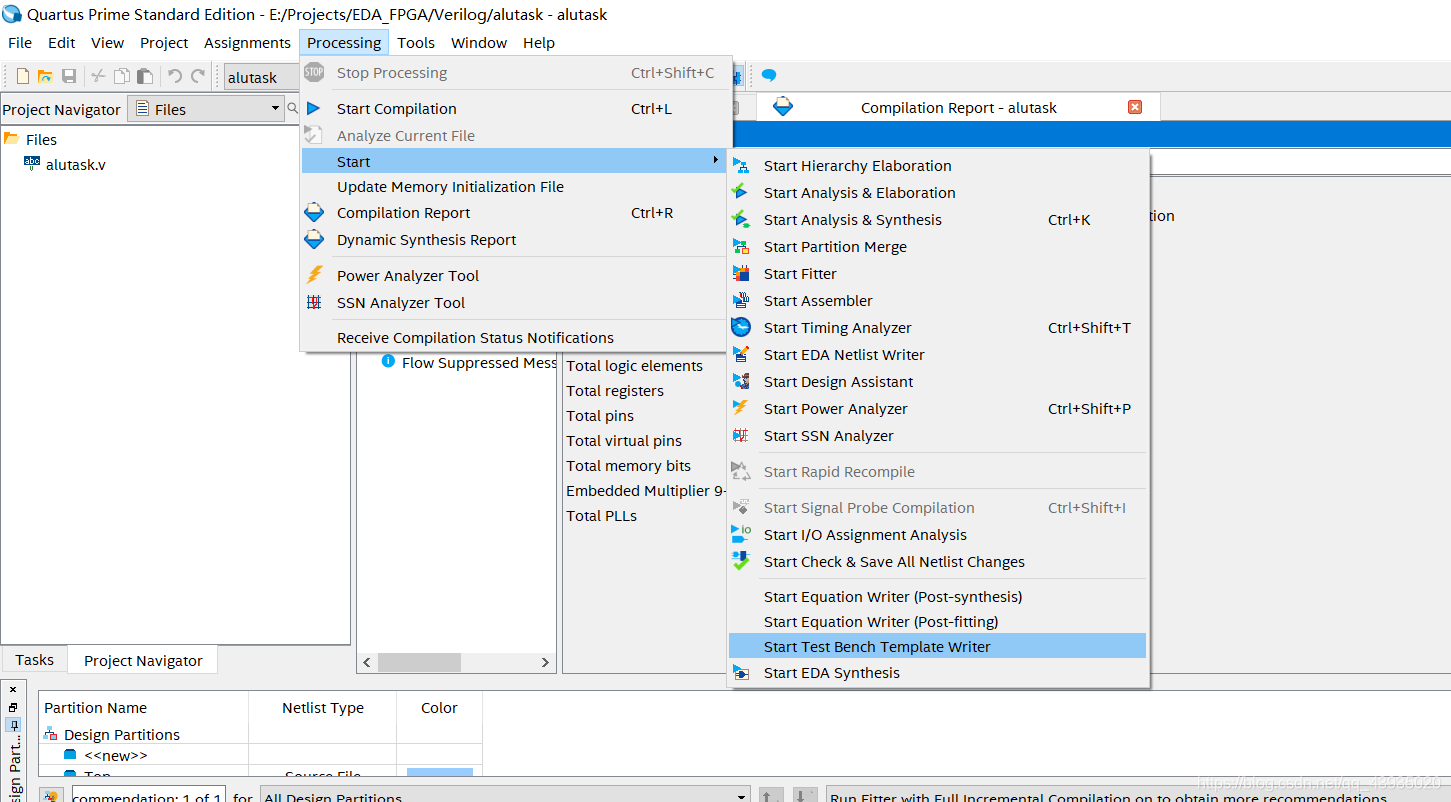

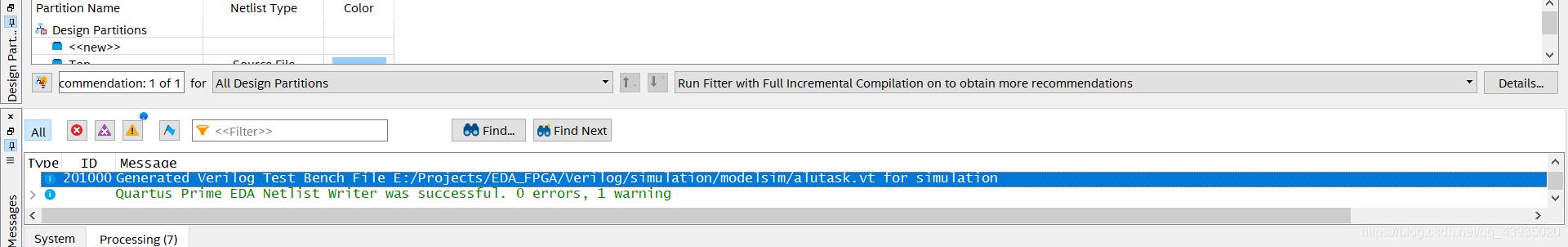

- Test Bench仿真脚本的建立:Processing—Start—Start Test Bench Template Writer

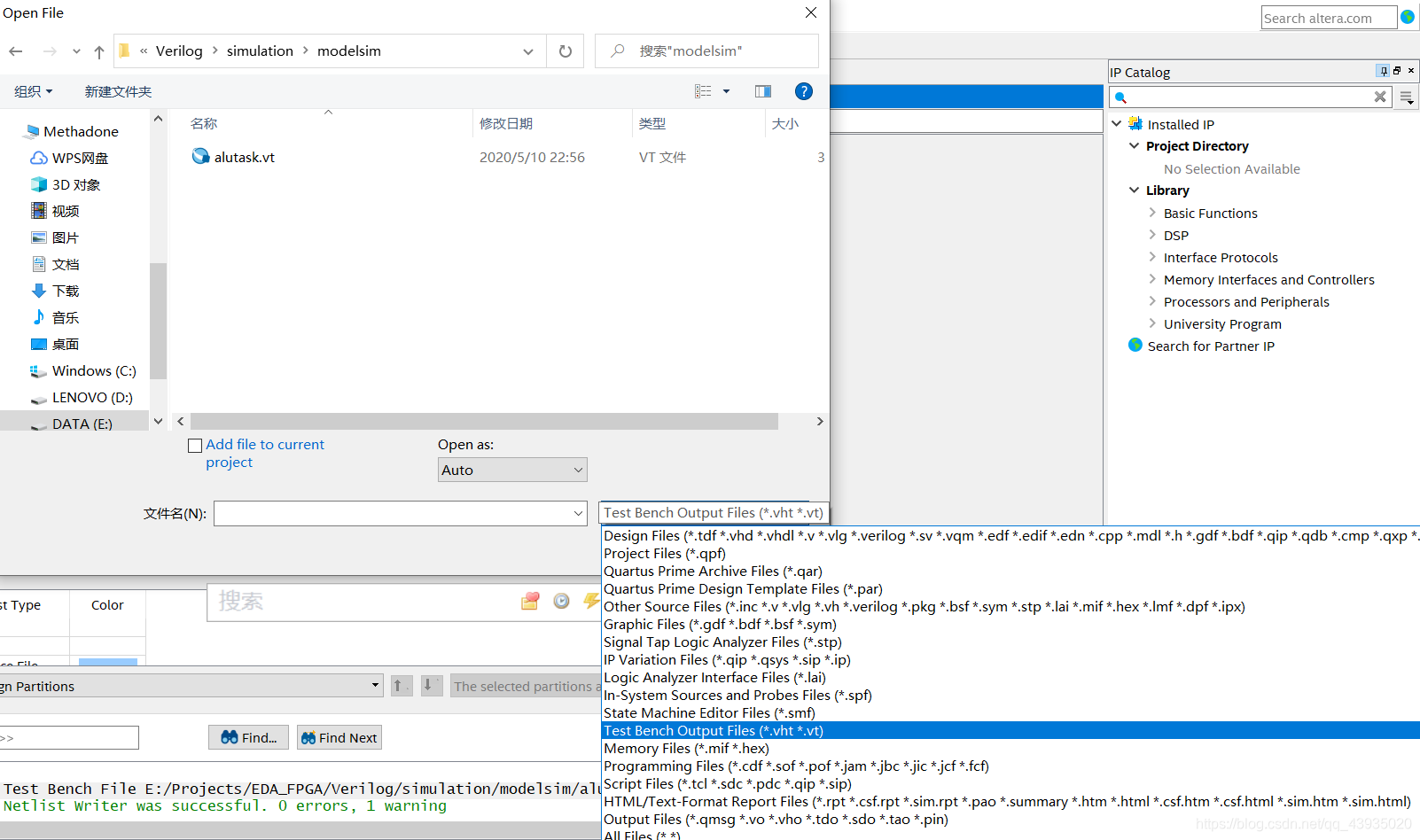

- 在底部信息栏中可以看到Test Bench仿真脚本的保存路径;再通过File—Open打开

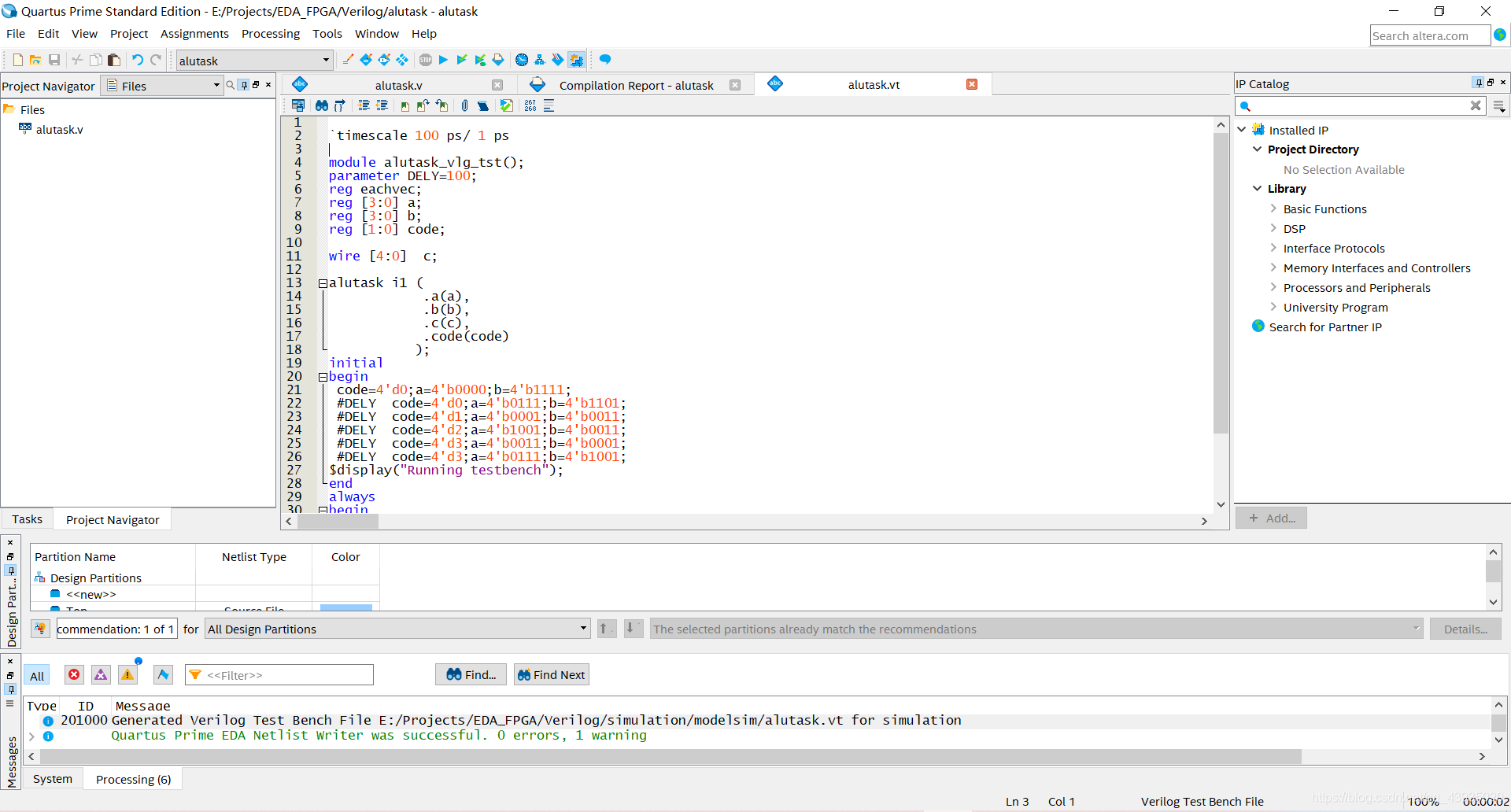

- 程序编写

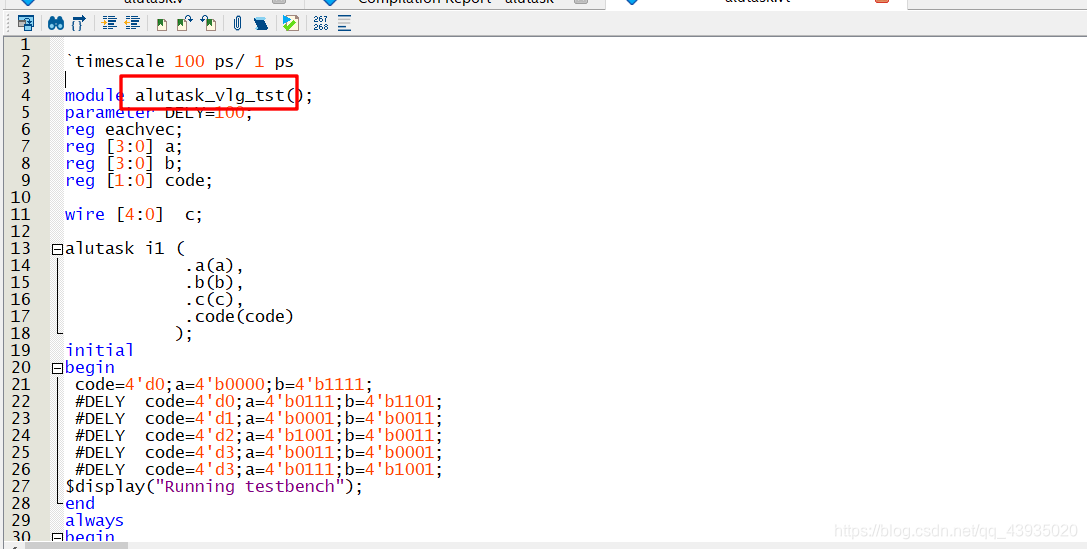

`timescale 100 ps/ 1 psmodule alutask_vlg_tst();parameter DELY=100;reg eachvec;reg [3:0] a;reg [3:0] b;reg [1:0] code; wire [4:0] c; alutask i1 ( .a(a), .b(b), .c(c), .code(code) );initial begin code=4'd0;a=4'b0000;b=4'b1111; #DELY code=4'd0;a=4'b0111;b=4'b1101; #DELY code=4'd1;a=4'b0001;b=4'b0011; #DELY code=4'd2;a=4'b1001;b=4'b0011; #DELY code=4'd3;a=4'b0011;b=4'b0001; #DELY code=4'd3;a=4'b0111;b=4'b1001; $display("Running testbench"); end always begin @eachvec; end endmodule - 保存后,再对脚本做进一步设置:

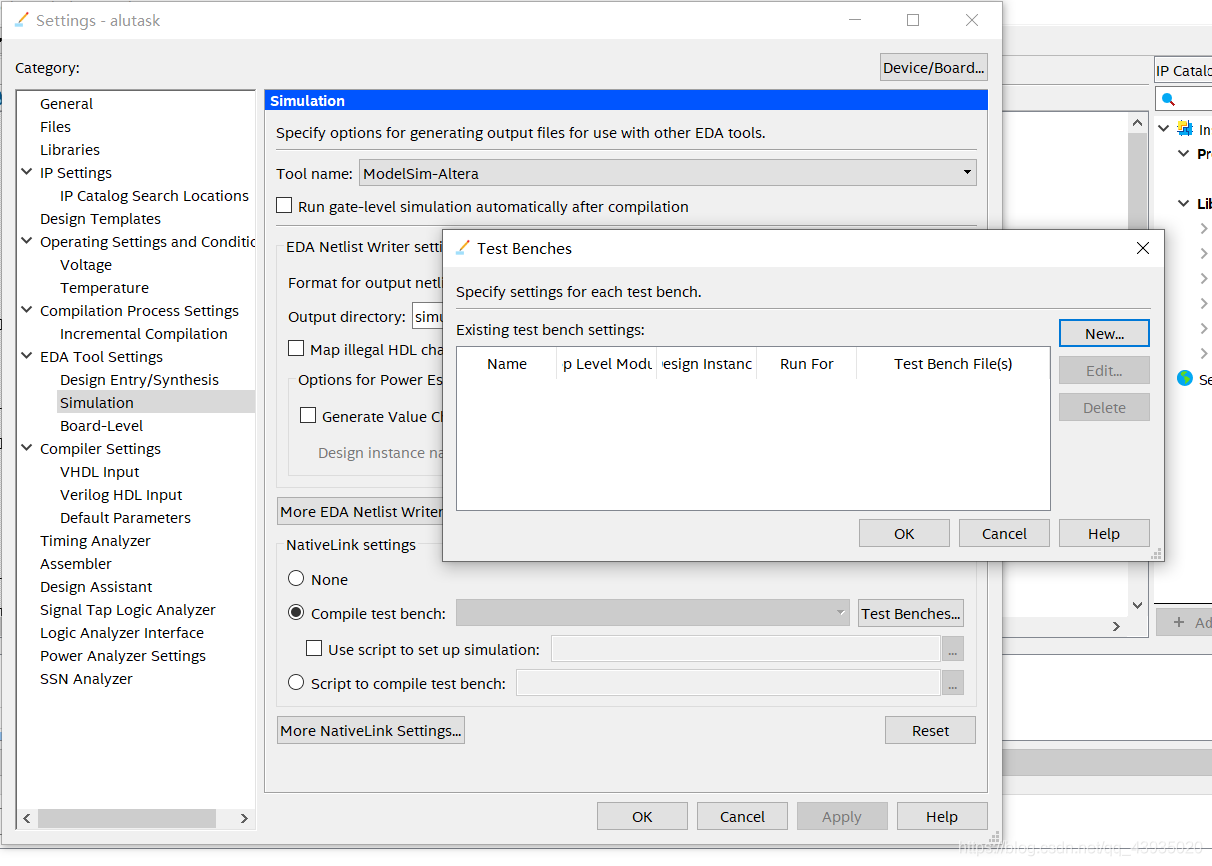

上图中的Test bench name必须与模块名(即下图红框中)相同

上图中的Test bench name必须与模块名(即下图红框中)相同

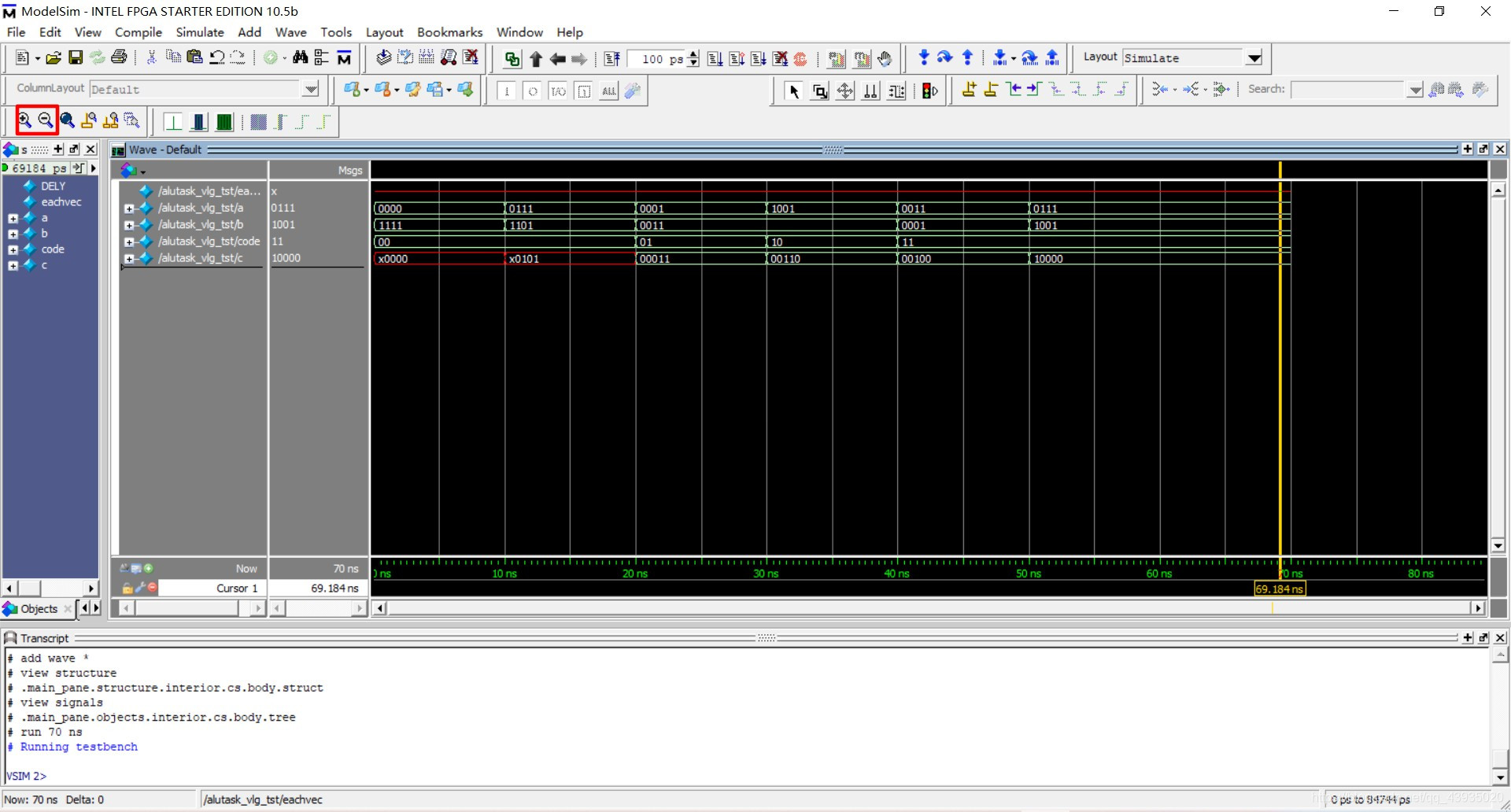

- 仿真:Tools—Run Simulation Tool—RTL Simulation:可以通过左上角的放大与缩小的到合适的图形。

转载地址:https://methadone-no1.blog.csdn.net/article/details/106044604 如侵犯您的版权,请留言回复原文章的地址,我们会给您删除此文章,给您带来不便请您谅解!

发表评论

最新留言

关注你微信了!

[***.104.42.241]2024年04月08日 02时41分05秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

linux中的sh脚本语法【转】

2019-05-02

区别数据结构中的堆栈与内存中的堆栈的个人总结【转】

2019-05-02

c++中冒号(:)和双冒号(::)的用法【转】

2019-05-02

python中各种下划线的含义

2021-07-05

《计算机视觉-一种现代方法(第2版)》读书笔记三:早期视觉(一幅图像)

2021-07-05

《计算机视觉-一种现代方法(第2版)》读书笔记六:应用之图像搜索和检索

2019-05-02

如何撰写高水平的学术论文

2019-05-02

谭浩强《C++面向对象程序设计》知识点总结

2019-05-02

分享一个关于介绍TextCNN和TextRNN的文章

2019-05-02

关于CNN中感受野的理解和计算方法

2019-05-02

java基础----RandomAccessFile

2019-05-02

__attribute__((packed))

2019-05-02

Android深入浅出之Binder机制

2019-05-02

linux查看硬件信息

2019-05-02

linux支持大于4G内存

2019-05-02

WM_GETINFO相关

2019-05-02

填入空隙(setbkcolor,setbkmode)

2019-05-02

[收藏] FC交换机基础知识详解

2019-05-02

关于数据中台系统,需要了解哪些技术?

2019-05-02

Linux调试工具

2019-05-02