【FPGA】学习笔记—{Verilog}—{一、Verilog设计初步}

用Verilog对该电路描述: 描述1:

用Verilog对该电路描述: 描述1:

发布日期:2021-07-01 03:12:28

浏览次数:2

分类:技术文章

本文共 2283 字,大约阅读时间需要 7 分钟。

【FPGA】学习笔记—{Verilog}—{一、Verilog设计初步}

1.1 Verilog简介

Verilog是一种硬件描述语言。

Idea→行为级描述→RTL描述→门(Gate)级网表→物理版图1.2 Verilog模块的结构

1.2.1 Verilog程序的特点

- ●Verilog程序的基本设计单元是“模块”(

module); ●每个模块的内容都嵌在module和endmodule之间; ●每个模块实现特定的功能。 - ●每个模块首先要进行端口定义; ●并说明输入和输出口(

input、output或inout); ●再对模块的功能进行定义。 - ● 除

endmodule等少数语句外,每个语句的最后必须有分号 。 - 注释: ●

//······●/*······*/

1.2.2 Verilog程序的4个主要部分

1、模块声明

1、模块声明包括:模块名字,模块输入、输出端口列表。

2、格式:module 模块名(端口1,端口2,端口3,……)

3、模块结束的标志为关键字 endmodule

2、端口(Port)定义

1、端口分类:

端口是模块与外界连接和通信的信号线

● input:输入端口

● output:输出端口 ● inout:双向端口 2、格式:input 端口名1,端口名2,…………端口名n; //输入端口 output 端口名1,端口名2,…………端口名n; //输出端口 inout 端口名1,端口名2,…………端口名n; //双向端口

3、注意:!!!

3、信号类型声明

●模块中所有用到的信号(包括端口信号、节点信号等)都必须进行数据类型的定义。

●Verilog语言提供的各种信号类型,分别模拟实际电路中的 各种物理连接和物理实体。 ●若信号的数据类型没有定义,则综合器将其默认为是wire型。 ●在Verilog-2001标准中,规定可以将端口声明和信号类型声明放在一条语句中完成。 ●端口声明和信号类型声明可以都放在模块列表中,而不是模块内部。 4、逻辑功能定义

1、用assign持续赋值语句定义。

●assign语句一般用于组合逻辑的赋值,称为持续赋值方式 ●格式:assign 结果信号名=表达式; 例:assign f=~((a&b)|(~(c&d))); 2、用always过程块定义。 ●格式: always @(敏感信号列表) begin //过程赋值 //if-else,case语句;for循环语句 //task,function调用 end

●例:见 例 描述3,4

3、调用元件(元件例化)。

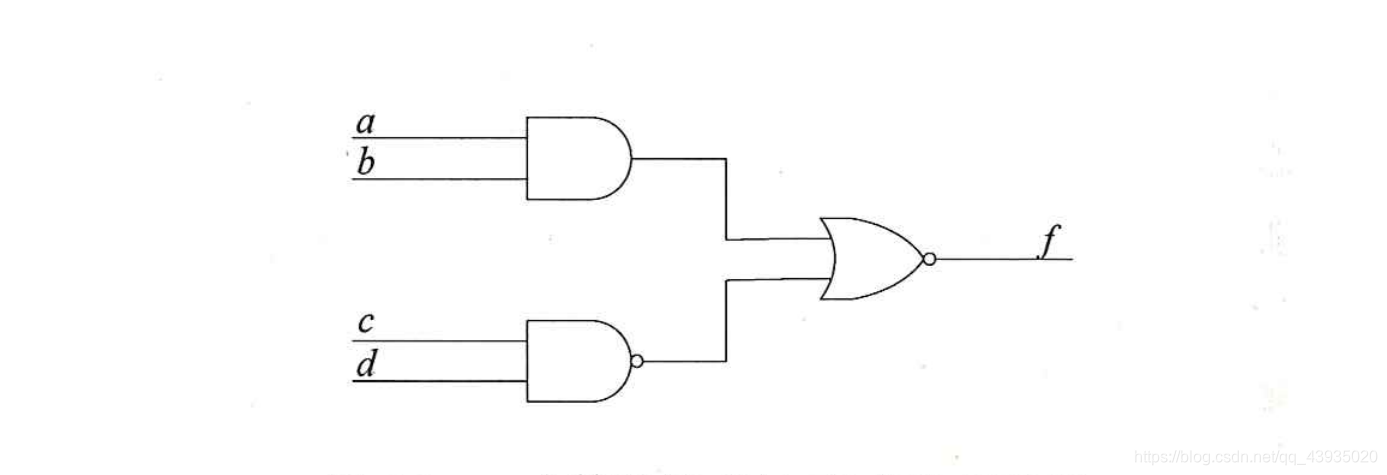

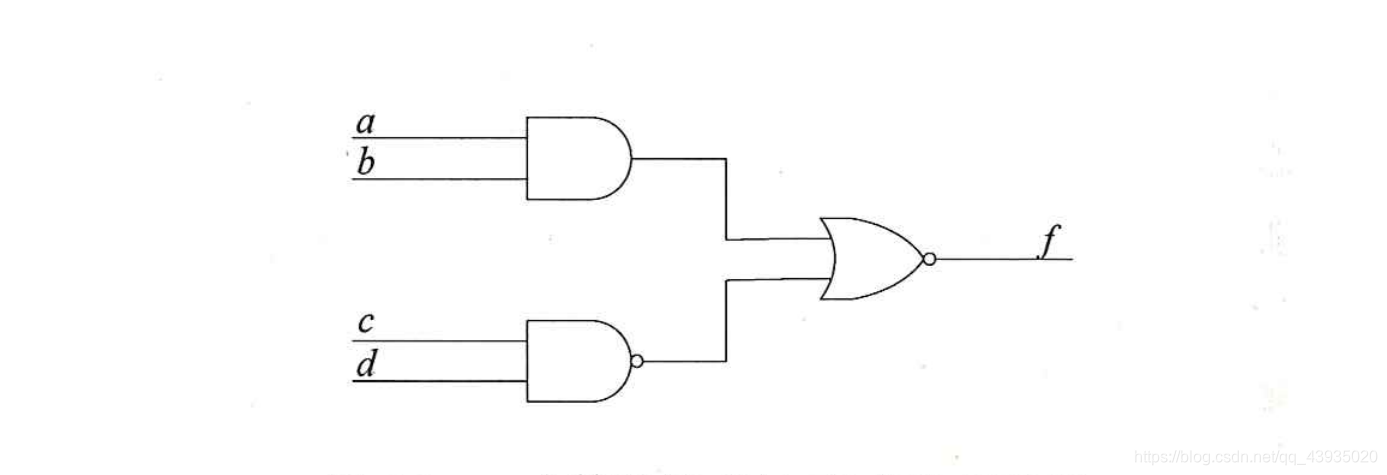

例 F = a b + c d ‾ ‾ F=\overline{ab+\overline{cd}} F=ab+cd  用Verilog对该电路描述: 描述1:

用Verilog对该电路描述: 描述1: module aoi(a,b,c,d,f); //模块名为aoi,端口列表a,b,c,d,finput a,b,c,d; //模块输入端为a,b,c,doutput f; //模块输出端为fwire a,b,c,d,f; //定义信号的数据类型 assign f=~((a&b)|(~(c&d))); //逻辑功能描述endmodule

描述2:

module aoi //将端口类型和信号类型的声明都放在模块列表 (input wire a,b,c,d, //在Verilog-2001标准中,规定可以将端口声明和信号类型声明放在一条语句中完成。 output wire f);assign f=~((a&b)|(~(c&d))); endmodule

描述3:

module aoi(a,b,c,d,f); input a,b,c,d; output f; reg f; //在always过程块中赋值的变量应定义为reg型always @(a or b or c or d) //always过程块及敏感信号列表 begin f=~((a&b)|(~(c&d))); //逻辑功能描述 endendmodule

描述4:

module aoi //模块声明采用Verilog-2001格式 (input a,b,c,d, output reg f); always @(*) //通配符,等价于a or b or c or d begin f=~((a&b)|(~(c&d))); //逻辑功能描述 endendmodule

1.3 Verilog基本组合电路设计

1.4 Verilog基本时序电路设计

转载地址:https://methadone-no1.blog.csdn.net/article/details/106259092 如侵犯您的版权,请留言回复原文章的地址,我们会给您删除此文章,给您带来不便请您谅解!

发表评论

最新留言

不错!

[***.144.177.141]2024年04月17日 06时27分33秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

开源全能播放器Vitamio的使用

2019-05-01

使用ViewPager加载页面出现空白

2019-05-01

ImageView scaleType

2019-05-01

RecyclerView notifyItem闪屏问题

2019-05-01

dubbo学习笔记 十一 dubbo-rpc之模块

2019-05-01

motan学习笔记 五 opentracing学习入门

2019-05-01

求列表最长子序列

2019-05-01

字符串的排序

2019-05-01

内存分配(mallloc,calloc,realloc,new)

2019-05-01

ffmpeg & mplayer & vlc 手册

2019-05-01

Go语言并发组件

2019-05-01

简析STUN协议

2019-05-01

使用 Minidumps 和 Visual Studio .NET 进行崩溃后调试

2019-05-01

Debug 和 Release 编译方式的本质区别

2019-05-01

struts返回xml数据例子

2019-05-01

内存对齐详解

2019-05-01

秋招总结(一)-C++归纳

2019-05-01

秋招总结(三)-操作系统归纳

2019-05-01

带缓冲I/O 和不带缓冲I/O的区别与联系

2019-05-01

LINUX CP命令详解

2019-05-01