FPGAVerilog语言要素

发布日期:2021-07-01 03:12:28

浏览次数:2

分类:技术文章

本文共 2627 字,大约阅读时间需要 8 分钟。

FPGAVerilog语言要素

2.1 概述

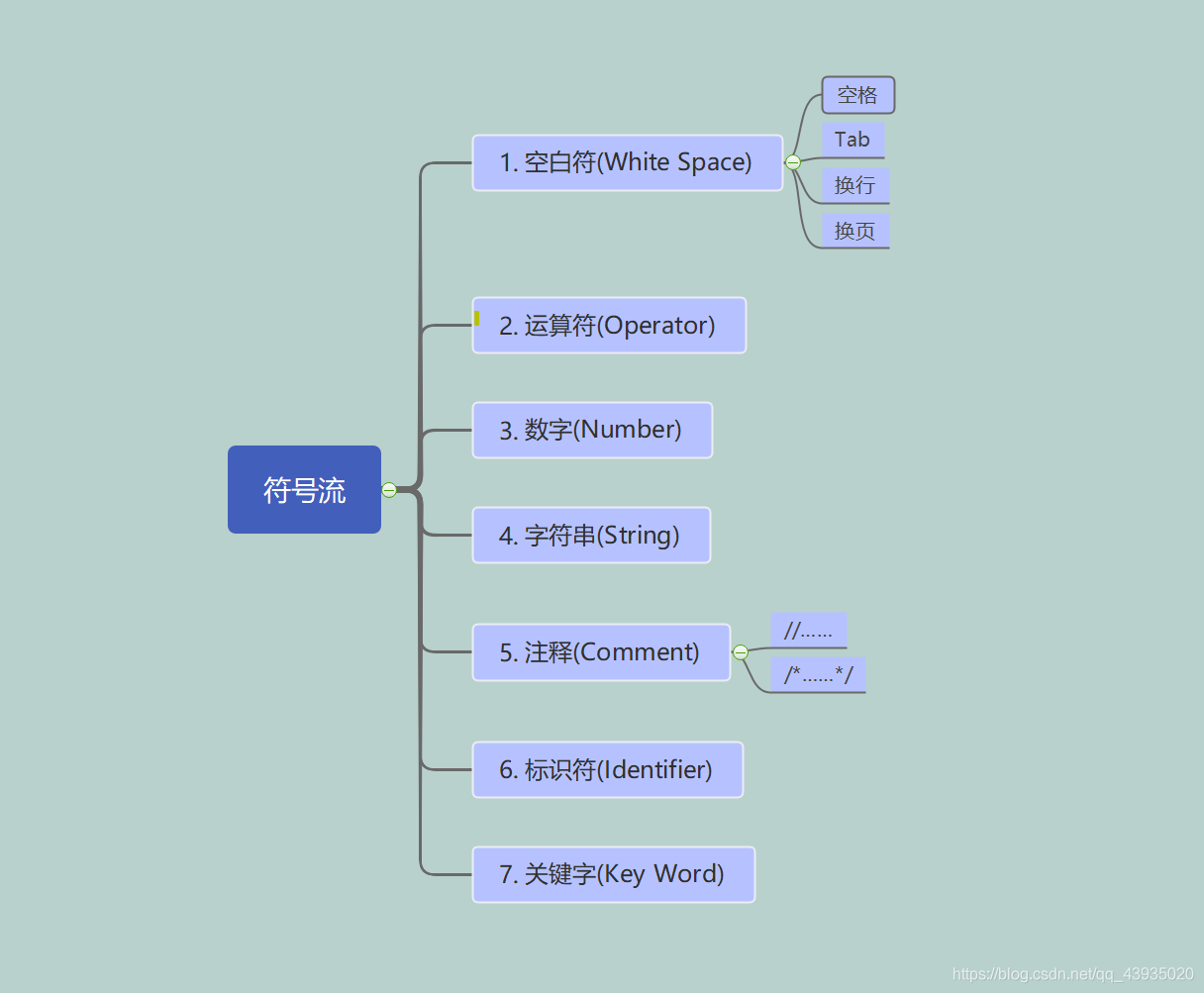

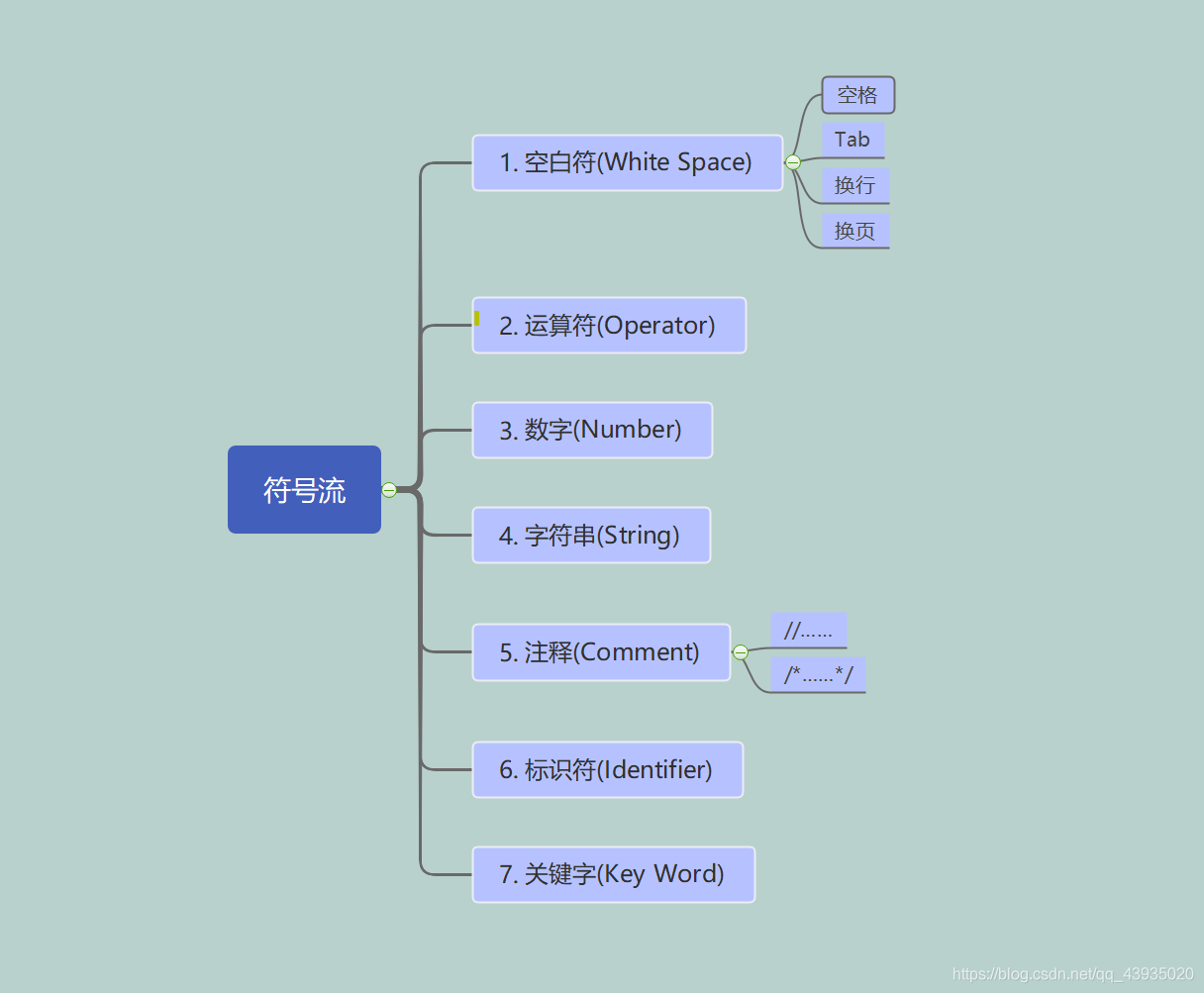

Verilog程序由各种符号流构成。

1、空白符(White Space)

●包括:空格、Tab、换行、、换页

●在综合时空白符被忽略。2、注释(Comment)

●单行注释://

●多行注释:/*……*/3、标识符(Identifier)

●标识符是给Verilog对象起的名字,模块、端口和实例的名字都是标识符。

●命名规则: ○可以是任意一组字母、数字以及符号“$”和“_”(下画线)的组合。 ○第一个字符必须是字母(a~ z,A~Z)或者是下画线“_” ○最长可以包含1023个字符。 ○标识符区分大小写。 ●转义标识符(Escaped identifiers) ○以"\"开头,以空白符结尾。 ○可以包含任意符号 ○反斜线和结束空白符并不是转义标识符的一部分。 ○\OutGate=OutGate 4、关键字(Key Word)

●关键字(保留字):Verilog语言内部已经使用的词。

●所有关键字都是小写。5、运算符(Operator)

2.2 常量

常量(Constant):在程序运行过程中,值不能被改变的量。Verilog中的常量主要有三种:

●整数;-------------可综合 ●实数;-------------不可综合 ●字符串。----------不可综合2.2.1 正数(Integer)

- 格式:

+/-'

即:

+/- <位宽> ' <进制> <数字>

●size为对应二进制的宽度;

●base为进制; ●value是基于 进制的数字序列。 ●4种进制: ○二进制(b或B); ○十进制(d或D,或默认); ○十六进制(h或H); ○八进制(o或O)。- Notes: ①在较长的数之间可用下画线分开。 ●下画线可以随意用在整数和实数中,本身无意义,用来提高可读性。 ●下画线只能用在具体数字之间; ●数字的第一个字符不能是下画线; ●下画线也不能用在位宽和进制处。 ②若未定义一个整数的位宽(unsized number),则默认为32位。

例

'b1101 //默认为32'b00000000_0000000_00000000_00001101 'haf //默认为32'b00000000_0000000_00000000_10101111

③定义的位宽与输入位宽不相等:

●若定义的位宽比数值的位数长,通常在左边填0补位;若数的最左边的一位为x或z,就相应地用x或者z在左边补位。例 10'b10 //左边补0, 00000_0001010'bx0x1 //左边补x, xxxxx_xx0x1

●若定义的位宽比数值的位数小,左边的位被截掉。

例 3'b1001_0011 //与3'b011相等5'H0FFF //与5'H1F相等

④高阻态的两种表示:

●? ●Z或者z ●两种表示方法完全等价,可相互替代。 ⑤x在二进制中代表一位x,在八进制中代表三位x,在十六进制中代表四位x,其所代表的宽度取决于所用的进制。(z同理)

例 8'h9x //等价于8'b1001_xxxx8'haz //等价于8'b1010_zzzz

⑥整数可以带符号(正负号),并且正负号应写在最左边。负数通常表示为二进制的补码形式。

⑦位宽和进制不声明,则默认是十进制的数。例 32 //表示十进制数32-15 //表示十进制数-15

⑧在位宽和'之间,进制和数值之间允许出现空格;但'和进制之间,数值之间不允许出现空格。

+/- <位宽> ' <进制> <数字>

⑨在Verilog-2001中扩展了带符号的整数的定义。

例 8'sh5a //一个8位的十六进制带符号整数5a

2.2.2 实数(Real)

- 格式: ①十进制表示法

例

2.05.6780.12. //'2.'为非法:小数点的两侧都必须有数字

②科学计数法

例 43_5.1e2 //其值为43510.09.6E2 //960.05E-4 //0.0005

- 实数转换为整数,实数通过四舍五入被转换为最相近的整数。

2.2.3 字符串(String)

①字符串是双引号内的字符序列。字符串不能分成多行书写。

②在Verilog中采用reg型变量来存储字符串。 例 reg [8*12:1] stringvar; //定义stringvar为宽度为8*12(96位)的reg型变量initial beginstringvar="Hello world!"; //"Hello world!"由12个字符构成的字符串end

③字符串用做Verilog表达式或赋值语句中的操作数

●此时,字符串被看作8位的ASCII码序列; ●在操作过程中,如果声明的reg型变量位数大于字符串的实际长度,则在赋值操作后,字符串变量的左端(即最高位)补0;若声明的reg型变量位数小于字符串实际长度,那么字符串的左端被截去。 ④特殊字符| 特殊字符 | 说明 |

|---|---|

| \n | 换行 |

| \t | Tab键 |

| \\ | 符号\ |

| \ " | 符号" |

| \ddd | 八进制数ddd对应的ASCII字符 |

例

\123 //八进制数123对应的ASCII字符是大写字母S

2.3 数据类型

2.3.1 net型

2.3.2 variable型

2.4 参数

2.4.1 参数parameter

2.4.2 Verilog-2001中的参数声明

2.4.3 参数的传递

2.4.4 localparam

2.5 向量

2.6 运算符

转载地址:https://methadone-no1.blog.csdn.net/article/details/106269786 如侵犯您的版权,请留言回复原文章的地址,我们会给您删除此文章,给您带来不便请您谅解!

发表评论

最新留言

做的很好,不错不错

[***.243.131.199]2024年04月11日 03时55分51秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

JSP简明教程(三):JSP隐含对象

2021-07-05

JSP简明教程(四):EL表达式语言、JavaBean、Cookie、Session

2019-05-02

JSP简明教程(五):高级特性

2019-05-02

JSP简明教程:汇总

2019-05-02

简化网站开发:SiteMesh插件

2019-05-02

Struts1和Struts2的区别

2019-05-02

Spring框架:Spring安全

2019-05-02

Webx框架:Spring Schema 和 Spring Ext

2019-05-02

Webx框架:依赖注入

2019-05-02

Webx框架:Pipeline简介

2019-05-02

Webx框架:RequestContext详解

2019-05-02

Webx框架:Valve详解

2019-05-02

Webx框架:ResourceLoader

2019-05-02

Webx框架:AutoConfig

2019-05-02

Webx框架:会话管理

2019-05-02

Webx框架:表单验证

2019-05-02

开发工具系列(一):Btrace——线上Debug工具

2019-05-02

线上操作使用tmux提高工作效率

2019-05-02

什么是RAID?RAID有什么用?RAID原理

2019-05-02